- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383645 > MT9161B (Mitel Networks Corporation) 5 Volt Multi-Featured Codec (MFC)(5V 多特性編解碼器) PDF資料下載

參數(shù)資料

| 型號: | MT9161B |

| 廠商: | Mitel Networks Corporation |

| 元件分類: | Codec |

| 英文描述: | 5 Volt Multi-Featured Codec (MFC)(5V 多特性編解碼器) |

| 中文描述: | 5伏多功能的編解碼器(MFC)中(5V的多特性編解碼器) |

| 文件頁數(shù): | 7/30頁 |

| 文件大小: | 154K |

| 代理商: | MT9161B |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

Advance Information

MT9160B/61B

85

supports a strobed data interface found on many

standard Codec devices. This interface is commonly

referred to as Simple Serial Interface (SSI). The

combination of ST-BUS and SSI provides a Flexible

Digital Interface (FDI) capable of supporting all Mitel

basic rate transmission devices as well as many

other 2B+D transceivers.

The required mode of operation is selected via the

CSL2-0 control bits (Control Register 2, address

04h). Pin definitions alter dependent upon the

operational mode selected, as described in the

following subsections as well as in the Pin

Description tables.

Quiet Code

The FDI can be made to send quiet code to the

decoder and receive filter path by setting the RxMute

bit high. Likewise, the FDI will send quiet code in the

transmit path when the TxMute bit is high. Both of

these control bits reside in Control Register 1 at

address 03h. When either of these bits are low their

respective paths function normally. The -Zero entry

of Table 1 is used for the quiet code definition.

ST-BUS Mode

The ST-BUS consists of output (DSTo) and input

(DSTi) serial data streams, in FDI these are named

Dout and Din respectively, a synchronous clock input

signal CLOCKin (C4i), and a framing pulse input

(F0i). These signals are direct connections to the

corresponding pins of Mitel basic rate devices. The

CSL2, CSL1 and CSL0 bits are set to 1 for ST-BUS

operation.

The data streams operate at 2048 kb/s and are Time

Division Multiplexed into 32 identical channels of 64

kb/s bandwidth. A frame pulse (a 244 nSec low going

pulse) is used to separate the continuous serial data

streams into the 32 channel TDM frames. Each

frame has a 125

μ

Second period translating into an 8

kHz frame rate. A valid frame begins when F0i is

logic low coincident with a falling edge of C4i. Refer

to figure 11 for detailed ST-BUS timing. C4i has a

frequency (4096 kHz) which is twice the data rate.

This clock is used to sample the data at the 3/4

bit-cell position on DSTi and to make data available

on DSTo at the start of the bit-cell. C4i is also used to

clock the MT9160B/61B internal functions (i.e.,

Filter/Codec, Digital gain and tone generation) and to

provide the channel timing requirements.

The MT9160B/61B uses only the first four channels

of the 32 channel frame. These channels are always

defined, beginning with Channel 0 after the frame

pulse, as shown in Figure 6 (ST-BUS channel

assignments). The MT9161B provides a delayed

frame pulse (F0od), 4 channels after the input frame

pulse.

The first two (D & C) Channels are enabled for use

by the DEN and CEN bits respectively, (Control

Register 2, address 04h). ISDN basic rate service

(2B+D) defines a 16 kb/s signalling (D) Channel. The

MT9160B/61B supports transparent access to this

signalling channel. ST-BUS basic rate transmission

devices, which may not employ a microport, provide

access to their internal control/status registers

through the ST-BUS Control (C) Channel. The

MT9160B/61B supports microport access to this

C-Channel.

DEN - D-Channel

In ST-BUS mode access to the D-Channel (transmit

and receive) data is provided through an 8-bit read/

write register (address 06h). D-Channel data is

accumulated in, or transmitted from this register at

the rate of 2 bits/frame for 16 kb/s operation (1 bit/

frame for 8 kb/s operation). Since the ST-BUS is

asynchronous, with respect to the microport, valid

access to this register is controlled through the use

of an interrupt (IRQ) output. D-Channel access is

enabled via the (DEn) bit.

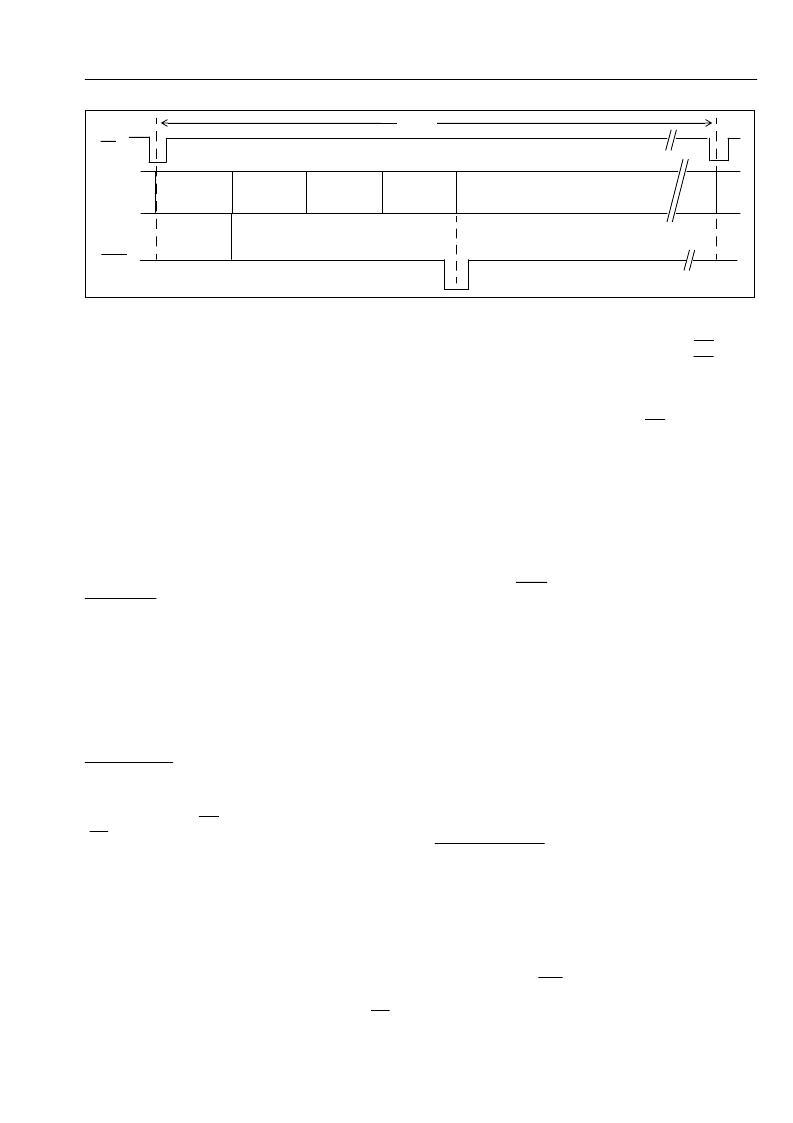

Figure 6 - ST-BUS Channel Assignment

F0i

DSTi,

DSTo

LSB first

for D-

Channel

MSB first for C, B1- & B2-

Channels

CHANNEL 0

D-channel

CHANNEL 1

C-channel

CHANNEL 2

B1-channel

CHANNEL 3

B2-channel

CHANNELS 4-31

Not Used

125

μ

s

F0od

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9162 | ISO2-CMOS 5 Volt Single Rail Codec |

| MT9171 | Digital Subscriber Interface Circuit with RxSB(數(shù)字用戶接口電路(帶接收同步位)) |

| MT9172 | Digital Network Interface Circuit with RxSB(數(shù)字網(wǎng)絡(luò)接口電路(帶接收同步位)) |

| MT9173AE | Digital Subscriber Interface Circuit with RxSB |

| MT9173AN | Digital Subscriber Interface Circuit with RxSB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9161BE | 制造商:Microsemi Corporation 功能描述:MULTI-FEATURED CODEC 24SOIC W - Rail/Tube |

| MT9161BN | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO2-CMOS 5 Volt Multi-Featured Codec (MFC) |

| MT9161BS | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:5 Volt Multi-Featured Codec (MFC) |

| MT9162 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:5 Volt Single Rail Codec |

| MT9162AE | 制造商:Microsemi Corporation 功能描述:CODEC 20PDIP - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。