- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359265 > MX98715AL SINGLE CHIP FAST ETHERNET NIC CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | MX98715AL |

| 英文描述: | SINGLE CHIP FAST ETHERNET NIC CONTROLLER |

| 中文描述: | 單晶片快速以太網(wǎng)卡控制器 |

| 文件頁數(shù): | 15/32頁 |

| 文件大小: | 215K |

| 代理商: | MX98715AL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

15

P/N:PM0537

REV. 1.2, FEB. 24, 1999

MX98715A

5.2.5 STATUS REGISTER ( CSR5 )

Field

28

27

Name

WKUPI

LC

Description

Wake Up event interrupt. Valid only if CSR16<22> bit is set.

100 Base-TX link status has changed either from pass to fail or fail to pass.

Read CSR12<1> for 100 Base-TX link status.

Error Bits, read only, indicating the type of error that casued fatal bus error.

Transmit Process State, read only bits indicating the state of transmit process.

Receive Process State, read only bits indicating the state of receive process.

Normal Interrupt Summary, is the logical OR of CSR5<0>, CSR5<2> and CSR5<6> and

CSR5<28>.

Abnormal Interrupt Summary, is the logical OR of CSR5<1>, CSR5<3>, CSR5<5>,

CSR5<7>, CSR5<8>, CSR5<9>, CAR5<10>, CSR5<11> and CSR5<13>, CSR5<27>.

Early receive interrupt, indicating the first buffer has been filled in ring mode, or 64 bytes

has been received in chain mode.

Fatal Bus Error, indicating a system error occured, MX98715A will disable all bus access.

Link Fail, indicates a link fail state in 10 Base-T port. This bit is valid only when CSR6<18>=0,

CSR14<8>=1, and CSR13<3>=0.

General Purpose Timer Expired, indicating CSR11 counter has expired.

25:23

22:20

19:17

16

EB

TS

RS

NIS

15

AIS

14

ERI

13

12

FBE

LF

11

GTE

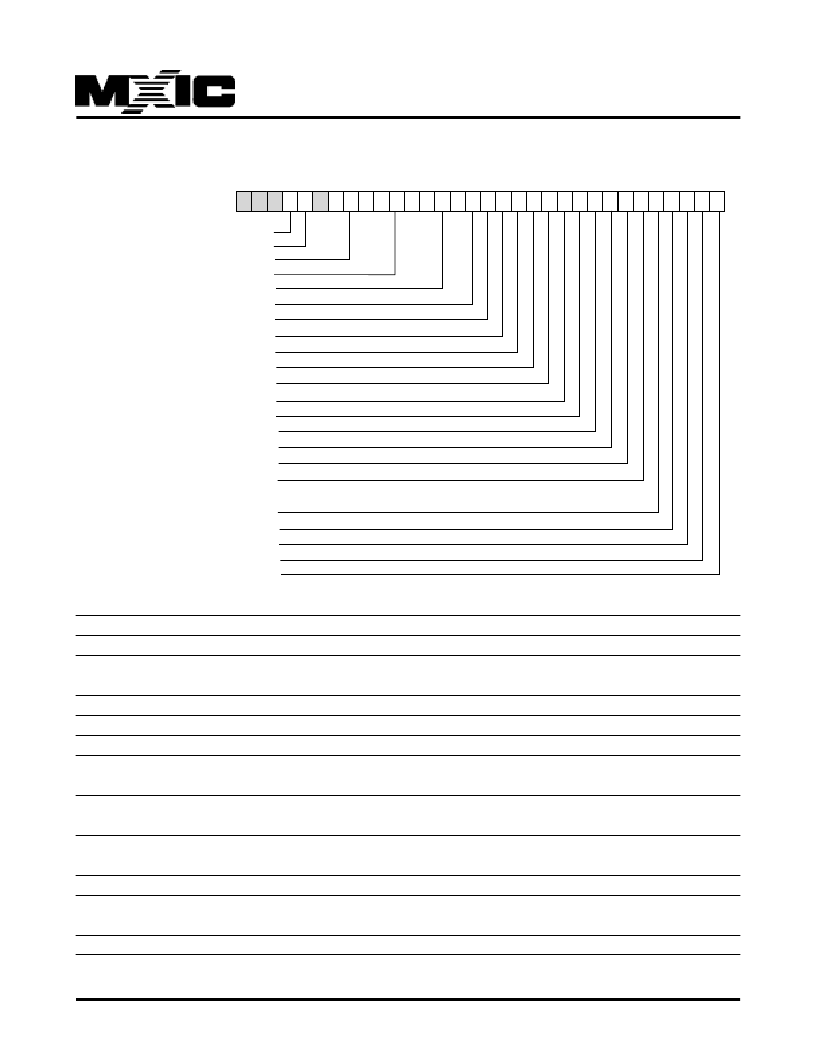

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RS-Receive Process State

NIS-Normal Interrupt Summary

AIS-Abnormal Interrupt Summary

ERI-Early Receive Interrupt

FBE-Fatal Bus Error

LF-Link Fail

ETI-Early Transmit Interrupt

RWT-Receive Watchdog Timeout

GTE-General Purpose Timer Expired

WKUPI-Wake Up event Interrupt

LC-Link Change

RPS-Receive Process Stopped

RU-Receive Buffer Unavailable

RI-Receive Interrupt

EB-Error Bits

TS-Transmit Process State

LPANCI-Link Pass/Autonegotiation

Completed Interrupt

UNF-Transmit Underflow

TJT-Transmit Jabber Timeout

TU-Transmit Buffer Unavailable

TPS-Transmit Process Stopped

TI-Transmit Interrupt

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MX98727 | SINGLE CHIP PCI/CARDBUS FAST ETHERNET CONTROLLER |

| MX98742 | FEBC 100 Base Fast Ethernet Bridge Controller |

| MX98902A(PLCC) | LAN Node Controller |

| MX98902A(PQFP) | LAN Node Controller |

| MX98902A(SQFP) | LAN Node Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MX98715BEC | 制造商:MCNIX 制造商全稱:Macronix International 功能描述:APPLICATION NOTE |

| MX98725 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE CHIP FAST ETHERNET NIC CONTROLLER |

| MX98726 | 制造商:MCNIX 制造商全稱:Macronix International 功能描述:SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER WITH uP INTERFACE |

| MX98726AEC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| MX98726EC | 制造商:MCNIX 制造商全稱:Macronix International 功能描述:SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER WITH uP INTERFACE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。