- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383705 > OQ2541BHP CLOCK/DATA RECOVERY|BIPOLAR|QFP|48PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | OQ2541BHP |

| 英文描述: | CLOCK/DATA RECOVERY|BIPOLAR|QFP|48PIN|PLASTIC |

| 中文描述: | 時鐘/數(shù)據(jù)恢復(fù)|雙極| QFP封裝| 48PIN |塑料 |

| 文件頁數(shù): | 10/40頁 |

| 文件大?。?/td> | 292K |

| 代理商: | OQ2541BHP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

2000 Sep 18

10

Philips Semiconductors

Product specification

SDH/SONET data and clock recovery unit

STM1/4/16 OC3/12/48 GE

OQ2541BHP; OQ2541BU

The LOS function will only work properly if the input signal

is larger than the input offset of the OQ2541B. Otherwise,

the signal will be masked by the input offset and

interpreted as consecutive bits of the same sign, thus

obstructing a proper LOS detection. In practice, an optical

front-enddevicewithanoiselevel(RMS value)largerthan

the specified offset of the OQ2541B will ensure a proper

LOS indication.

The LOS detection is BER related, but neither dependent

on the data stream content nor protocol. Therefore, an

SDH/SONET data stream is not a prerequisite for a proper

LOS function. Since the LOS function of the OQ2541B is

derived from digital signals, it is a good supplement to an

analog, amplitude based, LOS indication.

Pin LOS is an open-collector TTL compatible output.

A pull-up resistor is to be connected to a positive supply

voltage.

The LOS pin will be at a HIGH level (TTL) if the data signal

is absent on pins DIN and DINQ or if BER > 5

×

10

2

.

Otherwise, pin LOS will be at a LOW level if

BER < 1

×

10

3

.

Reference frequency select

A reference clock signal of 19.44 or 38.88 MHz must be

connected to pins CREF and CREFQ. It should be noted

that the reference frequency should be either

39.0625 or 19.53125 MHzinaGE system.Pin DREF19is

used to select the appropriate output frequency at

frequency divider 2 (see Table 2).

To minimize the adverse influence of reference clock

crosstalk, a differential signal with an amplitude from

75 to 150 mV (p-p) is advised.

Sincethereferenceclockisonlyusedasanacquisitionaid

for the PLL of the frequency window detector, the quality

of the reference clock (i.e. phase noise) is not important.

There is no phase noise specification imposed on the

reference clock generator and even frequency stability

may be in the order of 100 ppm. In general, most

inexpensive crystal-based oscillators are suitable.

When the OQ2541B is used in an application with a fixed

reference clock frequency, it is best to connect

pin DREF19 through a short track or a via to the ground

plane or pin V

EE

. If a selectable reference clock frequency

is required in the application, the pin can be controlled

through a low ohmic switching FET, e.g. BSH103 or

equivalent (low R

DSon

).

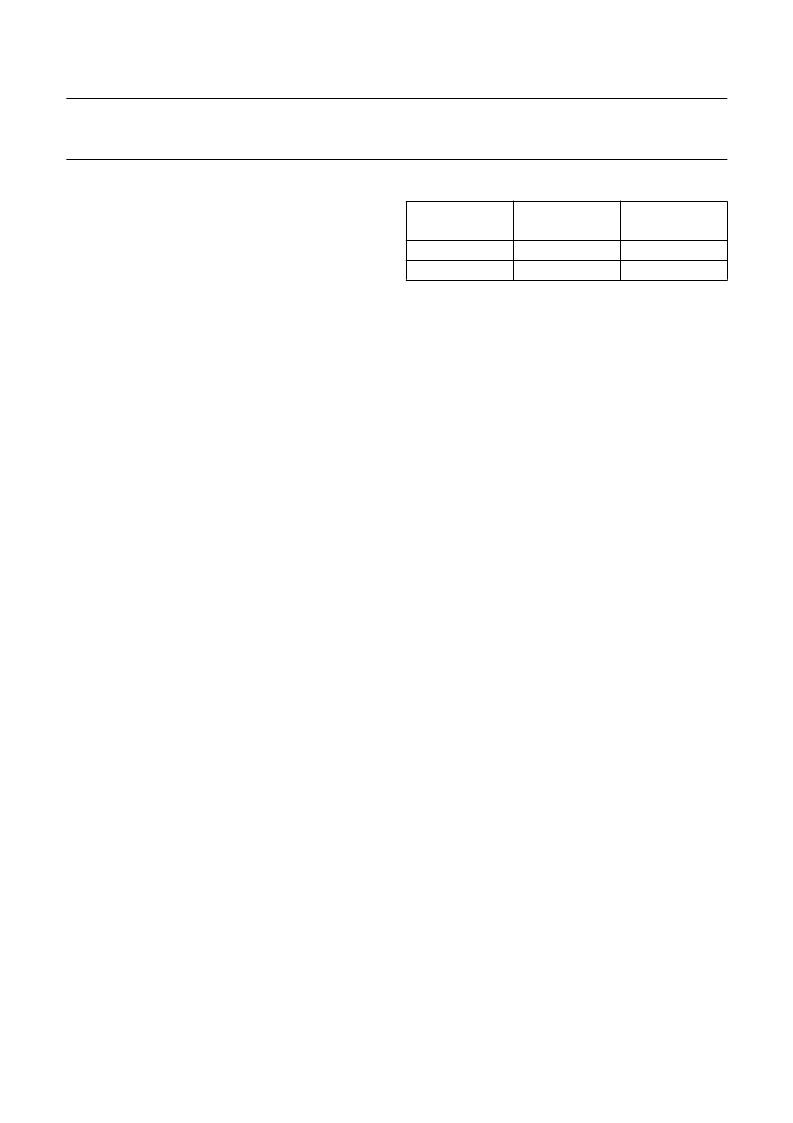

Table 2

Reference frequency selection

STM mode selection

The VCRO has a large tuning range. However, the

performance of the OQ2541B is optimized for

SDH/SONET, including GE bit rates.

Due to the nature of the PLL, the wide tuning range is a

necessity for proper lock behaviour over the guaranteed

temperature range, aging and batch to batch spread.

Though it might seem that the OQ2541B is capable of

recovering other bit rates than SDH/SONET and

GE bit rates(STM1/OC3, STM4/OC12,STM16/OC48and

1250 Mbits/s), the behaviour cannot be guaranteed.

The required SDH/SONET bit rate is selected by

connecting pins DOUT155, DOUT622 and DOUT1250

to ground or to the supply voltage V

EE

(see Table 3):

For STM16/OC48 (2488.32 Mbits/s) operation, all three

pins have to be connected to ground

For GE (1250 Mbits/s) operation, pin DOUT1250 has to

be connected to V

EE

For STM4/OC12 (622.08 Mbits/s) operation,

pins DOUT1250 and DOUT622 have to be connected

to V

EE

(the dividers are daisy chained)

ForSTM1/OC3(155,52 Mbits/s)operation,allthreepins

have to be connected to V

EE

.

The connections to V

EE

and ground carry a current of a

few mA and should have low resistance and inductance.

Therefore, short printed-circuit board tracks are

recommended. In some cases, a small decoupling

capacitor (approximately 100 pF) near the selection pins

might be necessary to provide a clean return path for

RF currents.

When the OQ2541B is used in an application with a fixed

data rate, it is best to connect pins DOUT155, DOUT622

and DOUT1250throughashorttrackoraviatotheground

plane or pin V

EE

. If a selectable bit rate is required in the

application, the pins can be controlled through low-ohmic

switching FETs, e.g. BSH103 or equivalent (low R

DSon

).

FREQUENCY

(MHz)

DIVISION

FACTOR

LEVEL ON PIN

DREF19

38.88

19.44

64

128

ground

V

EE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR22 | 2-input OR gate with 2x drive strength |

| OR2T04A-2PS84 | Field-Programmable Gate Arrays |

| OR2T04A-2BA100 | Field-Programmable Gate Arrays |

| OR2T04A-2BA100I | Field-Programmable Gate Arrays |

| OR2T04A-2BA144 | TIP REPLACEMENT CHISEL .062,0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OQ2541HP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:SDH/SONET data and clock recovery unit STM1/4/16 OC3/12/48 GE |

| OQ2541U | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:SDH/SONET data and clock recovery unit STM1/4/16 OC3/12/48 GE |

| OQ2545BHP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:SDH/SONET STM16/OC48 laser drivers |

| OQ2545HP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:SDH/SONET STM16/OC48 laser drivers |

| OQ8844 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital Servo Driver DSD-2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。