- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367641 > P12763EJ1V0AN00 MCU CMOS 28 LD 20MHZ 8K FLASH, -40C to +85C, 28-SPDIP, TUBE PDF資料下載

參數(shù)資料

| 型號: | P12763EJ1V0AN00 |

| 英文描述: | MCU CMOS 28 LD 20MHZ 8K FLASH, -40C to +85C, 28-SPDIP, TUBE |

| 中文描述: | uPC8119T和uPC8120T可變增益高頻硅單片放大器的AGC移動通信股 |

| 文件頁數(shù): | 9/19頁 |

| 文件大小: | 159K |

| 代理商: | P12763EJ1V0AN00 |

9

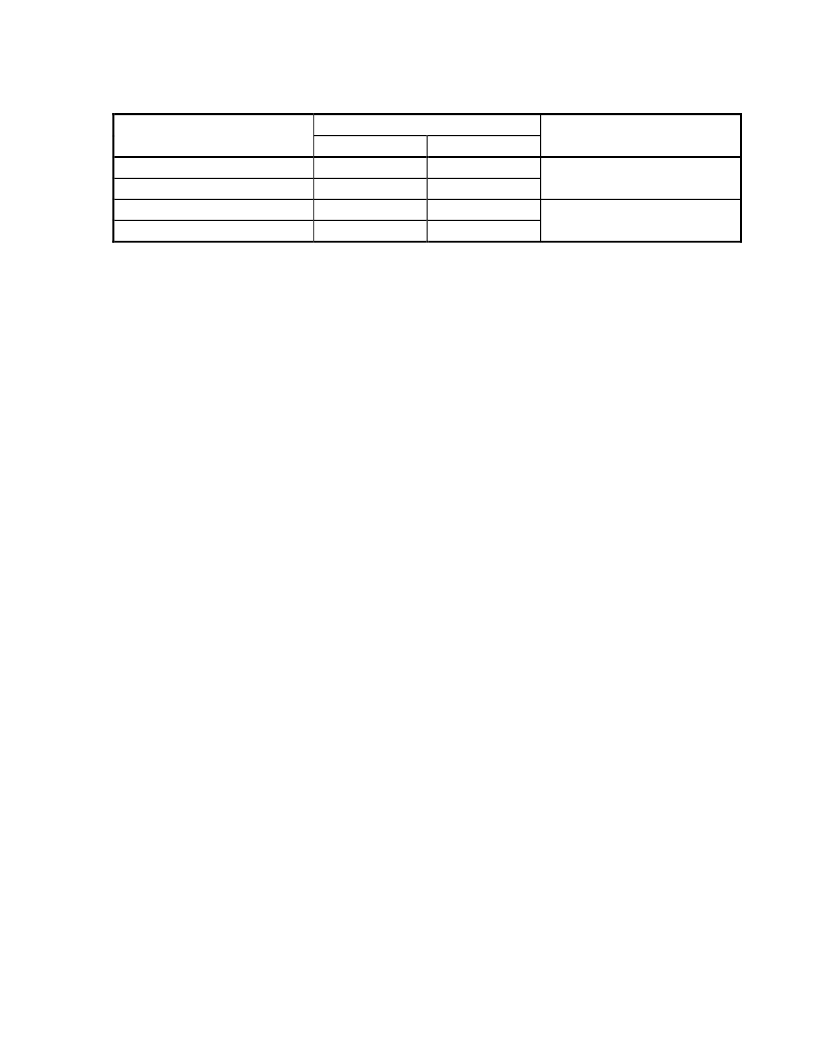

Table 4-1. Operational Differences between

P

PC8119T and

P

PC8120T

Operation

At maximum gain

At minimum gain

AGC control voltage (forward control)

Minimum

Maximum

P

PC8119T

Current into V

CC

pin

Minimum

Maximum

AGC control voltage (reverse control)

Maximum

Minimum

P

PC8120T

Current into output pin

Maximum

Minimum

5. EXTERNAL CIRCUIT CONFIGURATION

Figures 5-1 and 5-2 show an example of external circuit configuration and an example of configuration on an

evaluation board. With these ICs, the external capacitors connected to the V

CC

line and V

AGC

pin determine the

minimum gain, and the output matching circuit determines the maximum gain.

The external circuit of each pin is explained in detail below.

5.1 V

CC

Line and V

AGC

Pin (Determining minimum gain)

The output pin is the collector of the differential output transistor, so the bias is applied to the output pin by

connecting an inductor to the V

CC

line that is connected to the V

CC

pin, which is another collector of the differential

control circuit. Unless an external circuit is connected so that the V

CC

line is the load, therefore, the high-frequency

signal from the V

CC

pin leaks to the output pin at the minimum gain (because the current of the transistor at the

control side is maximum at the minimum gain). It is therefore necessary to optimize the feedback by inserting a

feedback capacitor between the V

CC

and AGC pins and by inserting a

S

type circuit consisting of a series inductor

and two parallel capacitors outside the feedback capacitor of the V

CC

pin. As a result, the leakage of the high-

frequency signal from the V

CC

pin can be attenuated. Without the feedback capacitance, the minimum gain increases

about 10 dB. Without the

S

type circuit, it increases about 20 dB. You, however, should note that this feedback

capacitance is affected by variations of the products if its value is too small to have frequency characteristics. In the

test circuit shown in the Data Sheet, each capacitance is 1000 pF which value is insensitive to characteristics in VHF

band. In the Data Sheet, a test circuit using a jumper line or pattern L as the series inductor of the

S

type circuit is

shown. This circuit is for simple evaluation and actually, a multi layer chip inductor of 4.7 nH can be used.

5.2 Output Matching (Determining maximum gain)

Because these ICs are of the open-collector output type, configure an LC matching circuit for RF impedance with

external components. The matching circuit consists of a parallel inductor at the V

CC

side and a series capacitor

toward the following stage. The collector of the output pin is biased by the voltage on the V

CC

pin via an inductor for

RF matching, as described above. Consequently, the inductor connected to the output pin has two effects: RF effect

of frequency matching and DC effect of applying a bias. Therefore, use a high-frequency inductor with a low DC

resistance. The LC value should be determined by referring to the S parameter at the maximum gain of the IC, so

that a power gain is obtained in a narrow region according to the operating frequency. Select a value so that S22

drops to –20 dBm at the maximum gain of the frequency band used. To bias the inductance connected to the output

pin, connect the output pin to the outside of the

S

ype circuit (not to the IC side) connected to the V

CC

line (otherwise,

the high-frequency signal from the V

CC

pin leaks out to the output pin and the minimum gain will not be available

below this leak level).

5.3 Input Pin

The impedance of the input pin is relatively low but is higher than 50

:

. The presence or absence of matching

should be determined by the impedance of the preceding stage. The bias must not be externally applied to input pin.

Part Number

DC Parameters

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P12C508 | 8-Pin, 8-Bit CMOS Microcontroller |

| P12 | ERSATZAKKU 12V |

| P1300SA | SIDACtor Device |

| P1100S | SIDACtor Device |

| P1100SCMC | solid state crowbar devices |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P128/BL/10M | 制造商:Adaptaflex 功能描述:25MM POLYAMIDE(PI) CONDUI |

| P1281-0151-01KBAS | 制造商:Measurement Specialties Inc 功能描述:PT, 0-1000 BAR, SINGLE SENSOR - Bulk |

| P1281-0151-1KBAS | 制造商:Measurement Specialties Inc 功能描述:PT, 0-1000 BAR, SINGLE SENSOR - Bulk |

| P128-1CCSF | 制造商:Carlisle Interconnect Components 功能描述:BETWEEN SERIES ADAPTER |

| P128-2CCSF | 制造商:Carlisle Interconnect Components 功能描述:BETWEEN SERIES ADAPTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。