- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367727 > P83C834 (NXP Semiconductors N.V.) 8-bit microcontrollers with LCD-driver PDF資料下載

參數(shù)資料

| 型號: | P83C834 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 8-bit microcontrollers with LCD-driver |

| 中文描述: | 8位微控制器與LCD驅(qū)動器 |

| 文件頁數(shù): | 14/36頁 |

| 文件大?。?/td> | 165K |

| 代理商: | P83C834 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

1997 Jul 03

14

Philips Semiconductors

Product specification

8-bit microcontrollers with LCD-driver

P83C434; P83C834

6.3.4

I

NTERRUPT

P

RIORITY

R

EGISTER

(IP)

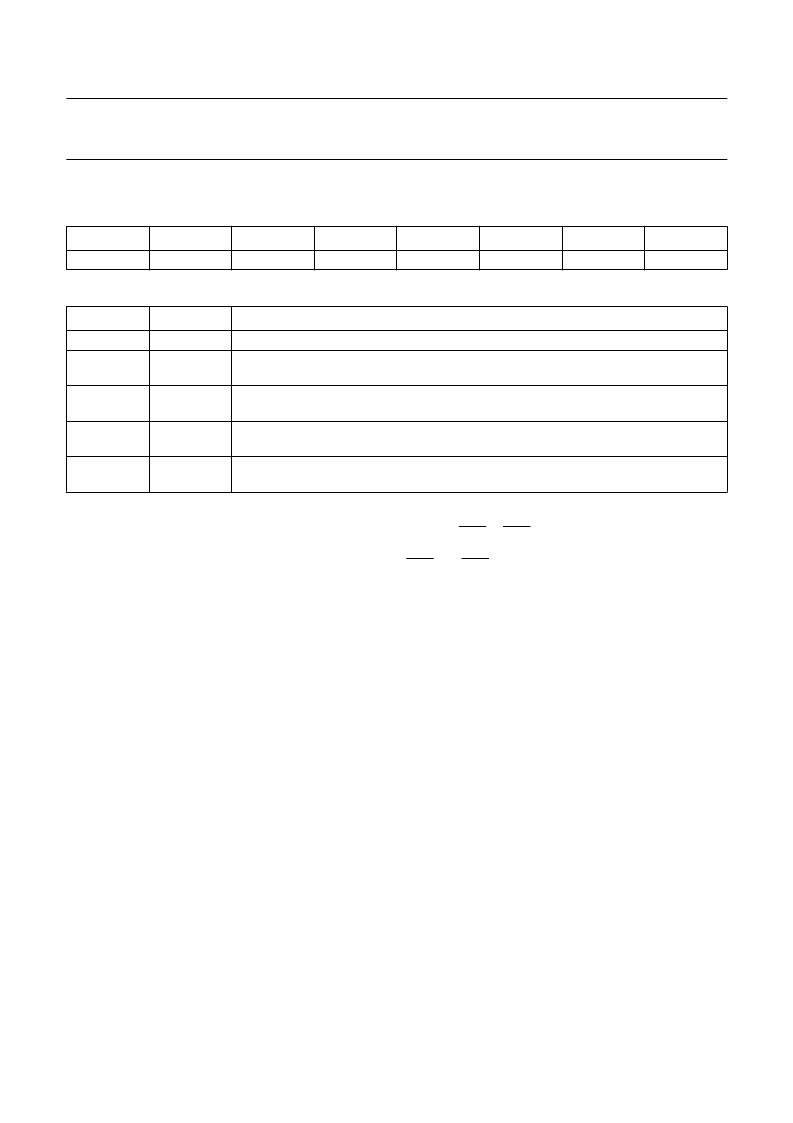

Table 8

Interrupt Priority Register (address B8H)

Table 9

Description of IP bits

7

6

5

4

3

2

1

0

PT1

PX1

PT0

PX0

BIT

SYMBOL

DESCRIPTION

7 to 4

3

PT1

Reserved.

Defines the Timer 1 Overflow Interrupt priority level

. When PT1 is HIGH, Timer 1

Overflow Interrupt is assigned a high priority level.

Defines the External Interrupt 1 priority level

. When PX1 is HIGH, External

Interrupt 1 is assigned a high priority level.

Defines the Timer 0 Overflow Interrupt priority level

. When PT0 is HIGH, Timer 0

Overflow Interrupt is assigned a high priority level.

Defines the External Interrupt 0 priority level

. When PX0 is HIGH, External

Interrupt 0 is assigned a high priority level.

2

PX1

1

PT0

0

PX0

6.4

Reduced power modes

6.4.1

I

DLE MODE

In the Idle mode, the CPU puts itself to sleep while all of

the on-chip peripherals remain active. The instruction to

invoke the Idle mode is the last instruction executed in the

normal operating mode before the Idle mode is activated.

The CPU contents, the on-chip RAM, and all of the special

function registers remain intact during this mode. The Idle

mode can be terminated either by any enabled interrupt (at

which time the process is picked up at the interrupt service

routine and continued), or by a hardware reset which starts

the processor in the same manner as a power-on reset.

6.4.2

P

OWER-DOWN MODE

In the Power-down mode, the CCO oscillator (processor

clock) is stopped; as the instruction to invoke Power-down

mode is the last instruction executed. Whether the 32 kHz

oscillator is stopped depends on bit RUN32 in the MCON

register (MCON5). The Power-down mode can be

terminated by a RESET in same way as in the 80C51 or in

addition by one of two external interrupts, INT0 or INT1.

A termination with an external interrupt does not affect the

internal data memory and does not affect the Special

Function Registers. This makes it possible to exit

Power-down without changing the port output levels.

To terminate the Power-down mode with an external

interrupt, INT0 or INT1 must be switched to level-sensitive

and must be enabled. The external interrupt input signal

INT0 and INT1 must be kept LOW until the oscillator has

restarted and stabilized. An instruction following the

instruction that puts the device in the Power-down mode

will be executed. The control bits for the reduced power

modes are in the Special Function Register PCON.

To wake-up the microcontroller by a reset, the RESET pin

must be kept HIGH for a minimum of 36

μ

s.

6.5

Reset

Reset is accomplished either at power-on when the supply

voltage rises above Power-on-reset threshold or by a

logic 1 signal at the RESET pin.

The Power-on-reset threshold is minimum 1.8 V and

maximum 3.0 V. The RESET signal should be active

(HIGH) for at least 2 machine cycles (24 oscillator

periods).

The reset algorithm puts registers and flip-flops in a

defined state (see 80C51 Family specification in “Data

Handbook IC20”and Section 6.6.1). The I/O ports are set

to a logic 1 at reset.

To wake-up from power-down the RESET signal must be

kept HIGH for a minimum of 36

μ

s.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83C834CFP | 8-bit microcontrollers with LCD-driver |

| P83C453EFAA | CMOS single-chip 8-bit microcontrollers |

| P87C453EBLKA | CMOS single-chip 8-bit microcontrollers |

| P87C453EFAA | CMOS single-chip 8-bit microcontrollers |

| P87C453EFLKA | CMOS single-chip 8-bit microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83C834CFP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-bit microcontrollers with LCD-driver |

| P83C845BBP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Microcontrollers for TV and video MTV |

| P83C851FBA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller with on-chip EEPROM |

| P83C851FBB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller with on-chip EEPROM |

| P83C851FBP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller with on-chip EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。