- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367727 > P87C453EFAA (NXP SEMICONDUCTORS) CMOS single-chip 8-bit microcontrollers PDF資料下載

參數(shù)資料

| 型號: | P87C453EFAA |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CMOS single-chip 8-bit microcontrollers |

| 中文描述: | OTPROM, 8 MHz, MICROCONTROLLER, PQCC68 |

| 封裝: | PLASTIC, SOT-168-3, MO-047AE, LCC-68 |

| 文件頁數(shù): | 8/23頁 |

| 文件大?。?/td> | 163K |

| 代理商: | P87C453EFAA |

Philips Semiconductors

Preliminary specification

80C453/83C453/87C453

CMOS single-chip 8-bit microcontrollers

1996 Aug 15

3-318

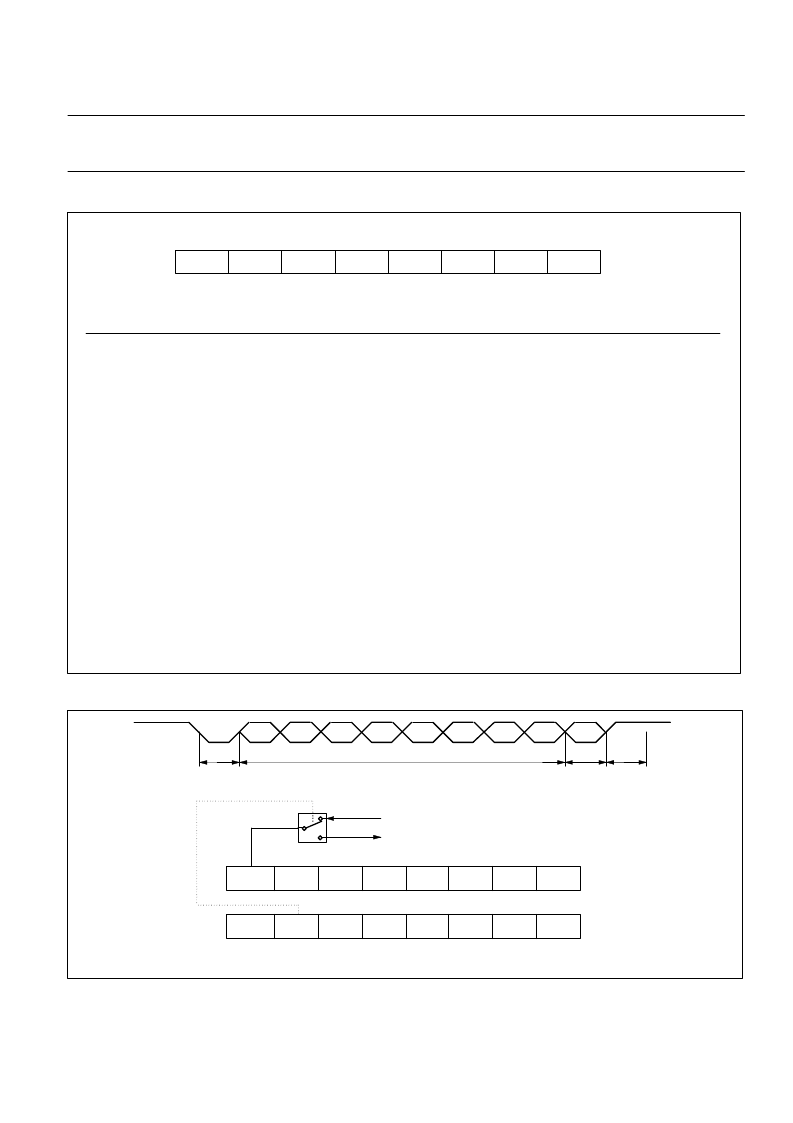

SCON

Address = 98H

Reset Value = 0000 0000B

SM0/FE

7

SM1

6

SM2

5

REN

4

TB8

3

RB8

2

Tl

1

Rl

0

Bit Addressable

(SMOD0 = 0/1)*

Symbol

Function

FE

Framing Error bit. This bit is set by the receiver when an invalid stop bit is detected. The FE bit is not cleared by valid

frames but should be cleared by software. The SMOD0 bit must be set to enable access to the FE bit.

Serial Port Mode Bit 0, (SMOD0 must = 0 to access bit SM0)

Serial Port Mode Bit 1

SM0

SM1

Mode

Description

Baud Rate**

0

0

0

shift register

f

OSC

/12

0

1

1

8-bit UART

variable

1

0

2

9-bit UART

f

OSC

/64 or f

OSC

/32

1

1

3

9-bit UART

variable

Enables the Automatic Address Recognition feature in Modes 2 or 3. If SM2 = 1 then Rl will not be set unless the

received 9th data bit (RB8) is 1, indicating an address, and the received byte is a Given or Broadcast Address.

In Mode 1, if SM2 = 1 then Rl will not be activated unless a valid stop bit was received, and the received byte is a

Given or Broadcast Address. In Mode 0, SM2 should be 0.

Enables serial reception. Set by software to enable reception. Clear by software to disable reception.

The 9th data bit that will be transmitted in Modes 2 and 3. Set or clear by software as desired.

In modes 2 and 3, the 9th data bit that was received. In Mode 1, if SM2 = 0, RB8 is the stop bit that was received.

In Mode 0, RB8 is not used.

Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the

other modes, in any serial transmission. Must be cleared by software.

Receive interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or halfway through the stop bit time in

the other modes, in any serial reception (except see SM2). Must be cleared by software.

SM0

SM1

SM2

REN

TB8

RB8

Tl

Rl

NOTE:

*SMOD0 is located at PCON6.

**f

OSC

= oscillator frequency

SU00043

Bit:

Figure 5. Serial Port Control Register (SCON)

SMOD1

SMOD0

OSF

POF

LVF

GF0

GF1

IDL

PCON

(87H)

SM0 / FE

SM1

SM2

REN

TB8

RB8

TI

RI

SCON

(98H)

D0

D1

D2

D3

D4

D5

D6

D7

D8

STOP

BIT

DATA BYTE

ONLY IN

MODE 2, 3

START

BIT

SET FE BIT IF STOP BIT IS 0 (FRAMING ERROR)

SM0 TO UART MODE CONTROL

0 : SCON.7 = SM0

1 : SCON.7 = FE

SU00044

Figure 6. UART Framing Error Detection

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P87C453EFLKA | CMOS single-chip 8-bit microcontrollers |

| P83C524GFA | 8-BIT MICROCONTROLLER |

| P80C32EBN | Microcontroller |

| P80C32EFN | Microcontroller |

| P80C32IBN | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P87C453EFL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P87C453EFLKA | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontrollers |

| P87C504GBA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P87C504GBB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| P87C504GBFA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。