- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367799 > PC7447VGH1200N (Atmel Corp.) PowerPC 7457 RISC Microprocessor PDF資料下載

參數(shù)資料

| 型號: | PC7447VGH1200N |

| 廠商: | Atmel Corp. |

| 英文描述: | PowerPC 7457 RISC Microprocessor |

| 中文描述: | 7457的PowerPC RISC微處理器 |

| 文件頁數(shù): | 27/66頁 |

| 文件大?。?/td> | 522K |

| 代理商: | PC7447VGH1200N |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

27

PC7457/47 [Preliminary]

5345B–HIREL–02/04

Notes:

1. This specification describes a logical offset between the internal clock edge used to

launch the L3 address and control signals (this clock edge is phase-aligned with the

processor clock edge) and the internal clock edge used to launch the L3_CLK[n] sig-

nals. With proper board routing, this offset ensures that the L3_CLK[n] edge will

arrive at the SRAM within a valid address window and provide adequate setup and

hold time. This offset is reflected in the L3 bus interface AC timing specifications, but

must also be separately accounted for in the calculation of sample points and, thus, is

specified here.

2. This specification is the delay from a rising or falling edge on the internal_L3_CLK

signal to the corresponding rising or falling edge at the L3CLK[n] pins.

3. This specification is the delay from a rising or falling edge of L3_ECHO_CLK[n] to

data valid and ready to be sampled from the FIFO.

Effects of L3OHCR Settings on

L3 Bus AC Specifications

The AC timing of the L3 interface can be adjusted using the L3 Output Hold Control

Register (L3OCHR).

Each field controls the timing for a group of signals. The AC timing specifications pre-

sented herein represent the AC timing when the register contains the default value of

0x0000_0000. Incrementing a field delays the associated signals, increasing the output

valid time and hold time of the affected signals. In the special case of delaying an

L3_CLK signal, the net effect is to decrease the output valid and output hold times of all

signals being latched relative to that clock signal. The amount of delay added is summa-

rized in Table 12 on page 28.

Note that these settings affect output timing parameters only and

don’t

impact input tim-

ing parameters of the L3 bus in any way.

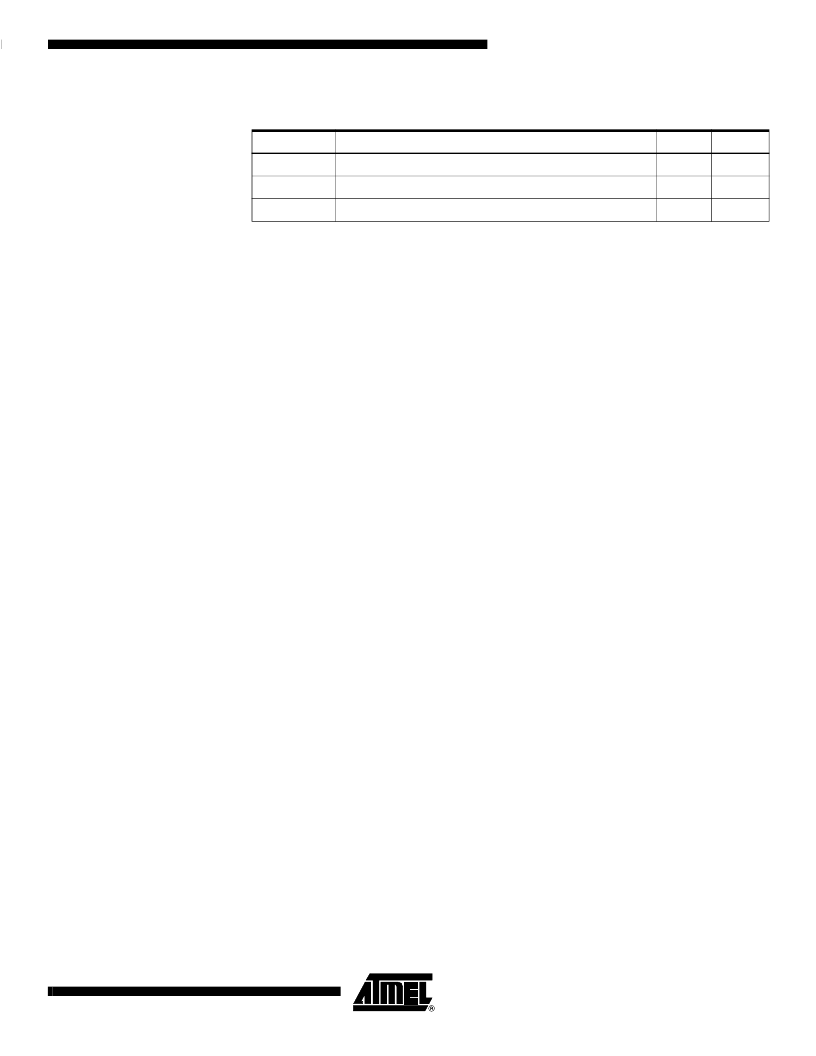

Table 11.

Sample Points Calculation Parameters

Symbol

Parameter

Max

Unit

t

AC

Delay from processor clock to internal_L3_CLK

(1)

3/4

t

L3_CLK

t

CO

Delay from internal_L3_CLK to L3_CLK[n] output pins

(2)

3

ns

t

ECI

Delay from L3_ECHO_CLK[n] to receive latch

(3)

3

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PC7447VGH933L | PowerPC 7457 RISC Microprocessor |

| PC7447VGH933N | PowerPC 7457 RISC Microprocessor |

| PC7457 | PowerPC 7457 RISC Microprocessor |

| PC7457MGU1000L | PowerPC 7457 RISC Microprocessor |

| PC7457MGU1000N | PowerPC 7457 RISC Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PC7447VGH933L | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 7457 RISC Microprocessor |

| PC7447VGH933N | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 7457 RISC Microprocessor |

| PC7448FGH1267ND | 制造商:e2v technologies 功能描述:PC7448FGH1267ND - Trays |

| PC7448MGH1000ND | 制造商:e2v technologies 功能描述:PC7448MGH1000ND - Trays |

| PC7448MGH1250ND | 制造商:e2v technologies 功能描述:MPU RISC 32BIT 0.09UM 1.25GHZ 1.5V/1.8V/2.5V 360HITCE CBGA - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。