- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄367799 > PC7457VGU1000N (Atmel Corp.) PowerPC 7457 RISC Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | PC7457VGU1000N |

| 廠(chǎng)商: | Atmel Corp. |

| 英文描述: | PowerPC 7457 RISC Microprocessor |

| 中文描述: | 7457的PowerPC RISC微處理器 |

| 文件頁(yè)數(shù): | 26/66頁(yè) |

| 文件大小: | 522K |

| 代理商: | PC7457VGU1000N |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)

26

PC7457/47 [Preliminary]

5345B–HIREL–02/04

L3 Bus AC Specifications

The PC7457 L3 interface supports three different types of SRAM: source-synchronous,

double data rate (DDR) MSUG2 SRAM, Late Write SRAMs, and pipeline burst (PB2)

SRAMs. Each requires a different protocol on the L3 interface and a different routing of

the L3 clock signals. The type of SRAM is programmed in L3CR[22:23] and the PC7457

then follows the appropriate protocol for that type. The designer must connect and route

the L3 signals appropriately for each type of SRAM. Following are some observations

about the L3 interface.

The routing for the point-to-point signals (L3_CLK[0:1], L3DATA[0:63], L3DP[0:7],

and L3_ECHO_CLK[0:3]) to a particular SRAM must be delay matched

For 1M byte of SRAM, use L3_ADDR[16:0] (L3_ADDR[0] is LSB)

For 2M bytes of SRAM, use L3_ADDR[17:0] (L3_ADDR[0] is LSB)

No pull-up resistors are required for the L3 interface

For high speed operations, L3 interface address and control signals should be a "T"

with minimal stubs to the two loads; data and clock signals should be point-to-point

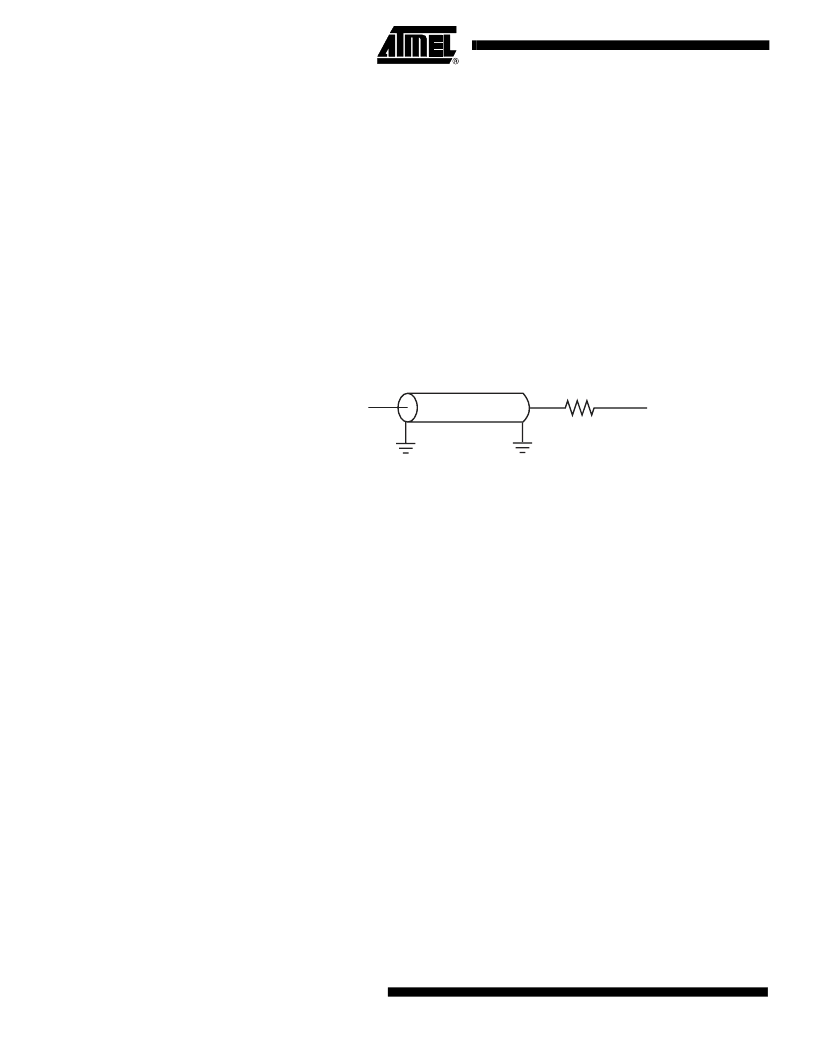

to their single load. Figure 12 shows the AC test load for the L3 interface.

Figure 12.

AC Test Load for the L3 Interface

In general, if routing is short, delay-matched, and designed for incident wave reception

and minimal reflection, there is a high probability that the AC timing of the PC7457 L3

interface will meet the maximum frequency operation of appropriately chosen SRAMs.

This is despite the pessimistic, guard-banded AC specifications (see Table 12 on page

28, Table 13 on page 29, and Table 14 on page 32), the limitations of functional testers

described in Section “L3 Clock AC Specifications” on page 24 and the uncertainty of

clocks and signals which inevitably make worst-case critical path timing analysis

pessimistic.

More specifically, certain signals within groups should be delay-matched with others in

the same group while intergroup routing is less critical. Only the address and control sig-

nals are common to both SRAMs and additional timing margin is available for these

signals. The double-clocked data signals are grouped with individual clocks as shown in

Figure 13 on page 30 or Figure 15 on page 33, depending on the type of SRAM. For

example, for the MSUG2 DDR SRAM (see Figure 13); L3DATA[0:31], L3DP[0:3], and

L3_CLK[0] form a closely coupled group of outputs from the PC7457; while

L3DATA[0:15], L3DP[0:1], and L3_ECHO_CLK[0] form a closely coupled group of

inputs.

The PC7450 RISC Microprocessor Family User’s Manual refers to logical settings called

"sample points" used in the synchronization of reads from the receive FIFO. The compu-

tation of the correct value for this setting is system-dependent and is described in the

PC7450 RISC Microprocessor Family User’s Manual.

Three specifications are used in this calculation and are given in Table 11 on page 27. It

is essential that all three specifications are included in the calculations to determine the

sample points as incorrect settings can result in errors and unpredictable behavior. For

more information, see the PC7450 RISC Microprocessor Family User’s Manual.

Z0 = 50

RL = 50

OVDD/

2

Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PC7457VGU1200L | PowerPC 7457 RISC Microprocessor |

| PC7457VGU1200N | PowerPC 7457 RISC Microprocessor |

| PC7457VGU933L | PowerPC 7457 RISC Microprocessor |

| PC7457VGU933N | PowerPC 7457 RISC Microprocessor |

| PC74HC4016 | SPST Analog Switch |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PC7457VGU1200L | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:PowerPC 7457 RISC Microprocessor |

| PC7457VGU1200N | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:PowerPC 7457 RISC Microprocessor |

| PC7457VGU933L | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:PowerPC 7457 RISC Microprocessor |

| PC7457VGU933N | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:PowerPC 7457 RISC Microprocessor |

| PC7457VGU933NC | 制造商:e2v technologies 功能描述:PC7457VGU933NC - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。