- 您現(xiàn)在的位置:買賣IC網 > PDF目錄367800 > PC755CMZFU300LE (ATMEL CORP) PowerPC 755/745 RISC Microprocessor PDF資料下載

參數(shù)資料

| 型號: | PC755CMZFU300LE |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PowerPC 755/745 RISC Microprocessor |

| 中文描述: | 32-BIT, 300 MHz, RISC PROCESSOR, PBGA360 |

| 封裝: | 25 X 25 MM, FLIP-CHIP, PLASTIC, BGA-360 |

| 文件頁數(shù): | 29/50頁 |

| 文件大小: | 1064K |

| 代理商: | PC755CMZFU300LE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

29

PC755/745

2138D–HIREL–06/03

Motorola is similarly limited by system constraints and cannot perform tests of the L2

interface on a socketed part on a functional tester at the maximum frequencies of Table

15. Therefore functional operation and AC timing information are tested at core-to-L2

divisors of 2 or greater. Functionality of core-to-L2 divisors of 1 or 1.5 is verified at less

than maximum rated frequencies.

L2 input and output signals are latched or enabled respectively by the internal L2CLK

(which is SYSCLK multiplied up to the core frequency and divided down to the L2CLK

frequency). In other words, the AC timings of Table 16 and Table 17 are entirely inde-

pendent of L2SYNC_IN. In a closed loop system, where L2SYNC_IN is driven through

the board trace by L2SYNC_OUT, L2SYNC_IN only controls the output phase of

L2CLKOUTA and L2CLKOUTB which are used to latch or enable data at the SRAMs.

However, since in a closed loop system L2SYNC_IN is held in phase alignment with the

internal L2CLK, the signals of Table 16 and Table 17 are referenced to this signal rather

than the not-externally-visible internal L2CLK. During manufacturing test, these times

are actually measured relative to SYSCLK.

The L2SYNC_OUT signal is intended to be routed halfway out to the SRAMs and then

returned to the L2SYNC_IN input of the PC755 to synchronize L2CLKOUT at the SRAM

with the processor’s internal clock. L2CLKOUT at the SRAM can be offset forward or

backward in time by shortening or lengthening the routing of L2SYNC_OUT to

L2SYNC_IN. See Motorola Application Note AN179/D “PowerPC

Backside L2 Timing

Analysis for the PCB Design Engineer.”

The L2CLKOUTA and L2CLKOUTB signals should not have more than two loads.

Notes:

1. L2CLK outputs are L2CLK_OUTA, L2CLK_OUTB, L2CLK_OUT and L2SYNC_OUT pins. The L2CLK frequency to core fre-

quency settings must be chosen so that the resulting L2CLK frequency and core frequency do not exceed their respective

maximum or minimum operating frequencies. The maximum L2LCK frequency will be system dependent. L2CLK_OUTA

and L2CLK_OUTB must have equal loading.

2. The nominal duty cycle of the L2CLK is 50% measured at midpoint voltage.

3. The DLL re

-

lock time is specified in terms of L2CLKs. The number in the table must be multiplied by the period of L2CLK to

compute the actual time duration in nanoseconds. Re

-

lock timing is guaranteed by design and characterization.

4. The L2CR[L2SL] bit should be set for L2CLK frequencies less than 110 MHz. This adds more delay to each tap of the DLL.

5. Allowable skew between L2SYNC_OUT and L2SYNC_IN.

6. This output jitter number represents the maximum delay of one tap forward or one tap back from the current DLL tap as the

phase comparator seeks to minimize the phase difference between L2SYNC_IN and the internal L2CLK. This number must

be comprehended in the L2 timing analysis. The input jitter on SYSCLK affects L2CLKOUT and the L2 address/data/control

signals equally and therefore is already comprehended in the AC timing and does not have to be considered in the L2 timing

analysis.

7. Guaranteed by design.

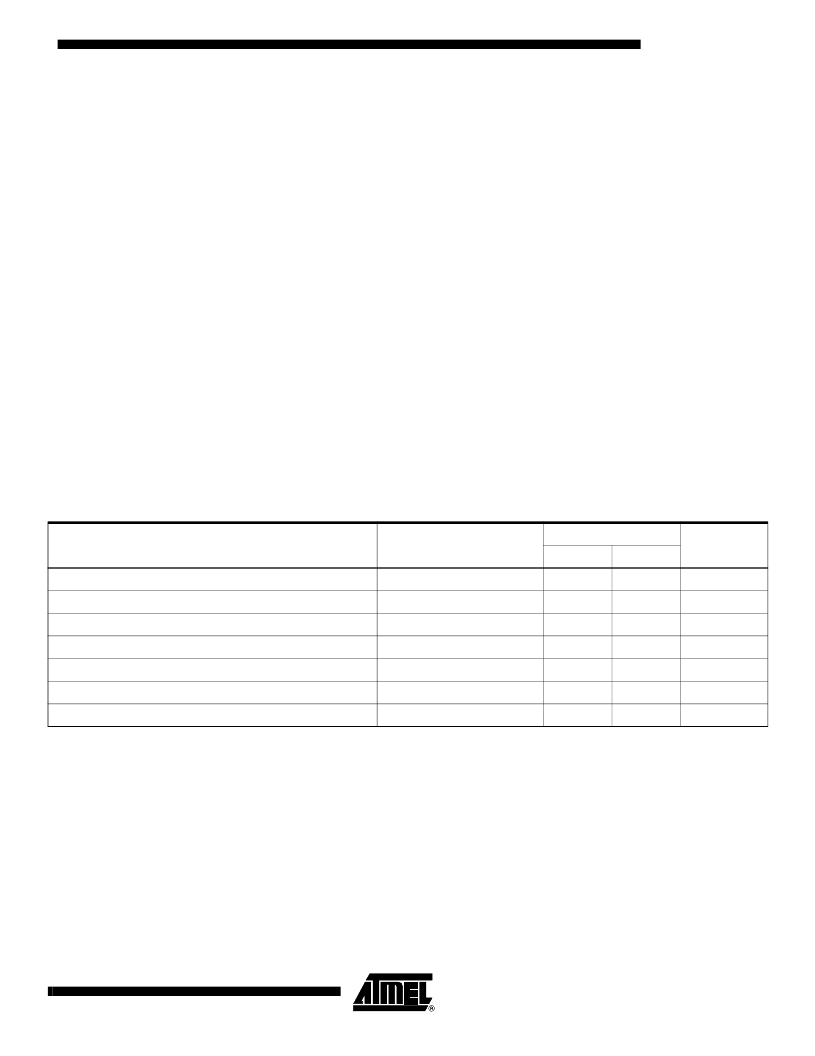

Table 15. L2CLK Output AC Timing Specification.

At

V

DD

= A

V

DD

= 2.0V 100 mV; -55

≤

T

j

≤

+125

°

C, OV

DD

= 3.3V

165 mV and OV

DD

= 1.8V 100 mV and OV

DD

= 2.0V 100 mV

Parameter

Symbols

All Speed Grades

Unit

Min

Max

L2CLK frequency

(1)(4)

f

L2CLK

80

450

MHz

L2CLK cycle time

t

L2CLK

2.5

12.5

ns

L2CLK duty cycle

(2)(7)

t

CHCL

/t

L2CLK

45

55

%

Internal DLL

-

relock time

(3)(7)

–

640

–

L2CLK

DLL capture window

(5)(7)

–

0

10

ns

L2CLKOUT output

-

to

-

output skew

(6)(7)

t

L2CSKW

–

50

ps

L2CLKOUT output jitter

(6)(7)

–

–

±150

ps

相關PDF資料 |

PDF描述 |

|---|---|

| PC755CVGSU300LE | PowerPC 755/745 RISC Microprocessor |

| PC755CVGSU350LE | PowerPC 755/745 RISC Microprocessor |

| PC755CVGSU366LE | PowerPC 755/745 RISC Microprocessor |

| PC755CVGSU400LE | PowerPC 755/745 RISC Microprocessor |

| PC812B | NPN-OUTPUT DC-INPUT OPTOCOUPLER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PC755CMZFU350LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CMZFU366LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CMZFU400LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

| PC755CVGH400LE | 制造商:e2v technologies 功能描述:POWERPC 755 32-BIT RISC MICROPROCESSOR - 400MHZ, 2.0V, HITCE, IND TEMP 制造商:e2v technologies 功能描述:MPU RISC 32BIT 0.22UM 400MHZ 2.5V/3.3V 360HITCE CBGA - Trays |

| PC755CVGHU300LE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:PowerPC 755/745 RISC Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復。