- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378045 > PCI6421 (Texas Instruments, Inc.) DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | PCI6421 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

| 中文描述: | 雙/單插槽CardBus和UltraMedia控制器 |

| 文件頁數(shù): | 44/204頁 |

| 文件大小: | 860K |

| 代理商: | PCI6421 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁

224

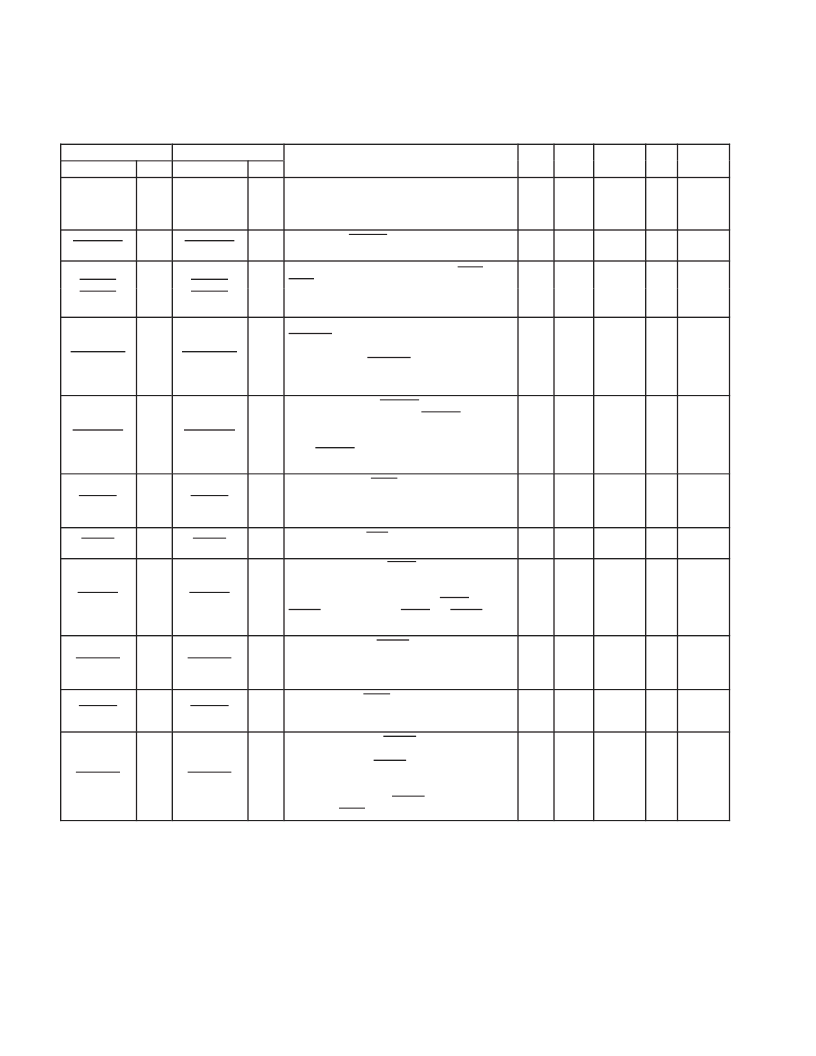

Table 214. CardBus PC Card Interface Control Terminals

If any CardBus PC Card interface control terminal is unused, then the terminal may be left floating.

SKT B TERMINAL

SKT A TERMINAL

DESCRIPTION

I/O

TYPE

INPUT

OUTPUT

PU/

PD

POWER

RAIL

NAME

NO.

NAME

NO.

A_CAUDIO

A02

B_CAUDIO

C17

CardBus audio. CAUDIO is a digital input signal from

a PC Card to the system speaker. The controller

supports the binary audio mode and outputs a binary

signal from the card to SPKROUT.

I

PCII4

PCIO4

PU3

VCCA/

VCCB

A_CBLOCK

E10

B_CBLOCK

J19

CardBus lock. CBLOCK is used to gain exclusive

access to a target.

I/O

PCII4

PCIO4

PU3

VCCA/

VCCB

A_CCD1

A_CCD2

C15

E05

B_CCD1

B_CCD2

N13

B17

CardBus detect 1 and CardBus detect 2. CCD1 and

CCD2 are used in conjunction with CVS1 and CVS2

to identify card insertion and interrogate cards to

determine the operating voltage and card type.

I

TTLI2

PU4

A_CDEVSEL

C09

B_CDEVSEL

H19

CardBus device select. The controller asserts

CDEVSEL to claim a CardBus cycle as the target

device. As a CardBus initiator on the bus, the

controller monitors CDEVSEL until a target responds.

If no target responds before timeout occurs, then the

controller terminates the cycle with an initiator abort.

I/O

PCII4

PCIO4

PU3

VCCA/

VCCB

A_CFRAME

C08

B_CFRAME

G19

CardBus cycle frame. CFRAME is driven by the

initiator of a CardBus bus cycle. CFRAME is asserted

to indicate that a bus transaction is beginning, and

data transfers continue while this signal is asserted.

When CFRAME is deasserted, the CardBus bus

transaction is in the final data phase.

I/O

PCII7

PCIO7

VCCA/

VCCB

A_CGNT

B09

B_CGNT

J15

CardBus bus grant. CGNT is driven by the controller

to grant a CardBus PC Card access to the CardBus

bus after the current data transaction has been

completed.

O

PCII7

PCIO7

VCCA/

VCCB

A_CINT

C04

B_CINT

B19

CardBus interrupt. CINT is asserted low by a CardBus

PC Card to request interrupt servicing from the host.

I

PCII4

PCIO4

PU3

VCCA/

VCCB

A_CIRDY

B08

B_CIRDY

J13

CardBus initiator ready. CIRDY indicates the ability of

the CardBus initiator to complete the current data

phase of the transaction. A data phase is completed

on a rising edge of CCLK when both CIRDY and

CTRDY are asserted. Until CIRDY and CTRDY are

both sampled asserted, wait states are inserted.

I/O

PCII4

PCIO4

PU3

VCCA/

VCCB

A_CPERR

F10

B_CPERR

J18

CardBus parity error. CPERR reports parity errors

during CardBus transactions, except during special

cycles. It is driven low by a target two clocks following

the data cycle during which a parity error is detected.

PCII4

PCIO4

PU3

VCCA/

VCCB

A_CREQ

E07

B_CREQ

E18

CardBus request. CREQ indicates to the arbiter that

the CardBus PC Card desires use of the CardBus bus

as an initiator.

I

PCII4

PCIO4

PU3

VCCA/

VCCB

A_CSERR

B03

B_CSERR

B18

CardBus system error. CSERR reports address parity

errors and other system errors that could lead to

catastrophic results. CSERR is driven by the card

synchronous to CCLK, but deasserted by a weak

pullup; deassertion may take several CCLK periods.

The controller can report CSERR to the system by

assertion of SERR on the PCI interface.

I

PCII4

PCIO4

PU3

VCCA/

VCCB

These terminals are reserved for the PCI6611 and PCI6411 controllers.

相關PDF資料 |

PDF描述 |

|---|---|

| PCI6611 | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

| PCI6621 | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

| PCI6515 | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

| PCI6515GHK | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

| PCI6515ZHK | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PCI6421GHK | 制造商:Texas Instruments 功能描述:DUAL/SGL SCKT CARDBUS AND ULTRAMEDIA CNTRLR W/ DEDICATED FLA - Trays |

| PCI6421ZHK | 制造商:Texas Instruments 功能描述:DUAL/SGL SCKT CARDBUS AND ULTRAMEDIA CNTRLR W/ DEDICATED FLA - Trays |

| PCI6466 | 制造商:PLX 制造商全稱:PLX 功能描述:Dual-Mode (Transparent & Non-Transparent) Universal FastLane⑩ 64-bit, 66MHz PCI-to-PCI Bridge |

| PCI6466-CB66BI | 功能描述:多路器開關 IC PCI to PCI Bridge 64 Bit 66MHz RoHS:否 制造商:Texas Instruments 通道數(shù)量:1 開關數(shù)量:4 開啟電阻(最大值):7 Ohms 開啟時間(最大值): 關閉時間(最大值): 傳播延遲時間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UQFN-16 |

| PCI6466-CB66BI G | 制造商:PLX Technology 功能描述:IC PCI TO PCI BRIDGE 380HSBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。