- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378045 > PCI6611 (Texas Instruments, Inc.) DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | PCI6611 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

| 中文描述: | 雙/單插槽CardBus和UltraMedia控制器 |

| 文件頁數(shù): | 37/204頁 |

| 文件大?。?/td> | 860K |

| 代理商: | PCI6611 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁

217

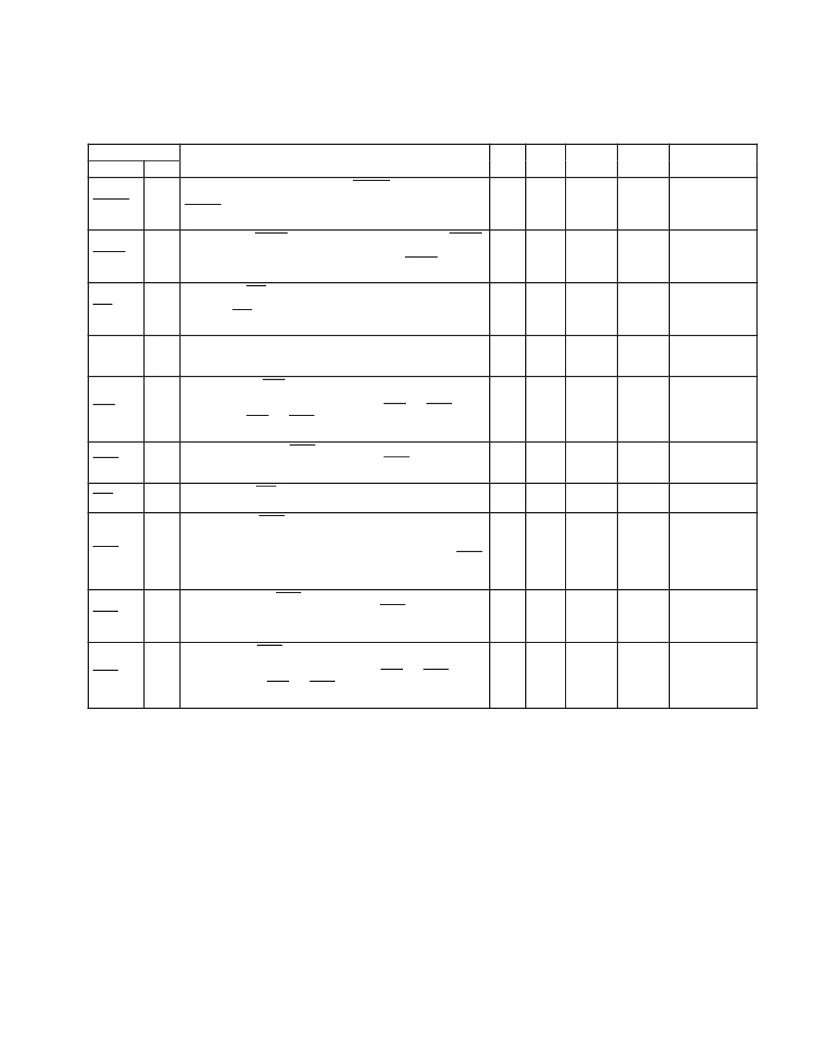

Table 28. PCI Interface Control Terminals

Internal pullup/pulldown resistors and pin strapping are not applicable for the PCI interface control terminals.

TERMINAL

DESCRIPTION

I/O

TYPE

INPUT

OUTPUT

POWER

RAIL

EXTERNAL

COMPONENTS

NAME

NO.

DEVSEL

N08

PCI device select. The controller asserts DEVSEL to claim a PCI cycle

as the target device. As a PCI initiator on the bus, the controller monitors

DEVSEL until a target responds. If no target responds before timeout

occurs, then the controller terminates the cycle with an initiator abort.

I/O

PCII3

PCIO3

VCCP

Pullup resistor per

PCI specification

FRAME

V07

PCI cycle frame. FRAME is driven by the initiator of a bus cycle. FRAME

is asserted to indicate that a bus transaction is beginning, and data

transfers continue while this signal is asserted. When FRAME is

deasserted, the PCI bus transaction is in the final data phase.

I/O

PCII3

PCIO3

VCCP

Pullup resistor per

PCI specification

GNT

T02

PCI bus grant. GNT is driven by the PCI bus arbiter to grant the

controller access to the PCI bus after the current data transaction has

completed. GNT may or may not follow a PCI bus request, depending on

the PCI bus parking algorithm.

I

PCII3

VCCP

IDSEL

W05

Initialization device select. IDSEL selects the controller during

configuration space accesses. IDSEL can be connected to one of the

upper 24 PCI address lines on the PCI bus.

I

PCII3

VCCP

IRDY

U07

PCI initiator ready. IRDY indicates the ability of the PCI bus initiator to

complete the current data phase of the transaction. A data phase is

completed on a rising edge of PCLK where both IRDY and TRDY are

asserted. Until IRDY and TRDY are both sampled asserted, wait states

are inserted.

I/O

PCII3

PCIO3

VCCP

Pullup resistor per

PCI specification

PERR

V08

PCI parity error indicator. PERR is driven by a PCI controller to indicate

that calculated parity does not match PAR when PERR is enabled

through bit 6 of the command register (PCI offset 04h, see Section 4.4).

I/O

PCII3

PCIO3

VCCP

Pullup resistor per

PCI specification

REQ

U01

PCI bus request. REQ is asserted by the controller to request access to

the PCI bus as an initiator.

O

PCIO3

VCCP

SERR

U08

PCI system error. SERR is an output that is pulsed from the controller

when enabled through bit 8 of the command register (PCI offset 04h,

see Section 4.4) indicating a system error has occurred. The controller

need not be the target of the PCI cycle to assert this signal. When SERR

is enabled in the command register, this signal also pulses, indicating

that an address parity error has occurred on a CardBus interface.

O

PCIO3

VCCP

Pullup resistor per

PCI specification

STOP

W08

PCI cycle stop signal. STOP is driven by a PCI target to request the

initiator to stop the current PCI bus transaction. STOP is used for target

disconnects and is commonly asserted by target devices that do not

support burst data transfers.

I/O

PCII3

PCIO3

VCCP

Pullup resistor per

PCI specification

TRDY

R08

PCI target ready. TRDY indicates the ability of the primary bus target to

complete the current data phase of the transaction. A data phase is

completed on a rising edge of PCLK when both IRDY and TRDY are

asserted. Until both IRDY and TRDY are asserted, wait states are

inserted.

I/O

PCII3

PCIO3

VCCP

Pullup resistor per

PCI specification

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI6621 | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

| PCI6515 | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

| PCI6515GHK | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

| PCI6515ZHK | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

| PCI7610LQFP | PC Card, UltraMedia, and Integrated 1394a-2000 OHCI Two-Port PHY/Link-Layer Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI6611GHK | 制造商:Texas Instruments 功能描述:DUAL/SGL SCKT CARDBUS AND ULTRAMEDIA CNTRLR W/ DEDICATED FLA - Trays |

| PCI6611ZHK | 制造商:Texas Instruments 功能描述:DUAL/SGL SCKT CARDBUS AND ULTRAMEDIA CNTRLR W/ DEDICATED FLA - Trays |

| PCI6612ZHK | 功能描述:外圍驅(qū)動器與原件 - PCI Integrated single socket RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI6620 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL SOCKET CARDBUS AND SMART CARD CONTROLLER WITH DEDICATED SD/MS-PRO SOCKETS |

| PCI6620GHK | 功能描述:外圍驅(qū)動器與原件 - PCI Integrated 2-Slot PC Card RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。