- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378045 > PCI6611 (Texas Instruments, Inc.) DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | PCI6611 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

| 中文描述: | 雙/單插槽CardBus和UltraMedia控制器 |

| 文件頁數(shù): | 81/204頁 |

| 文件大小: | 860K |

| 代理商: | PCI6611 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁當(dāng)前第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁

45

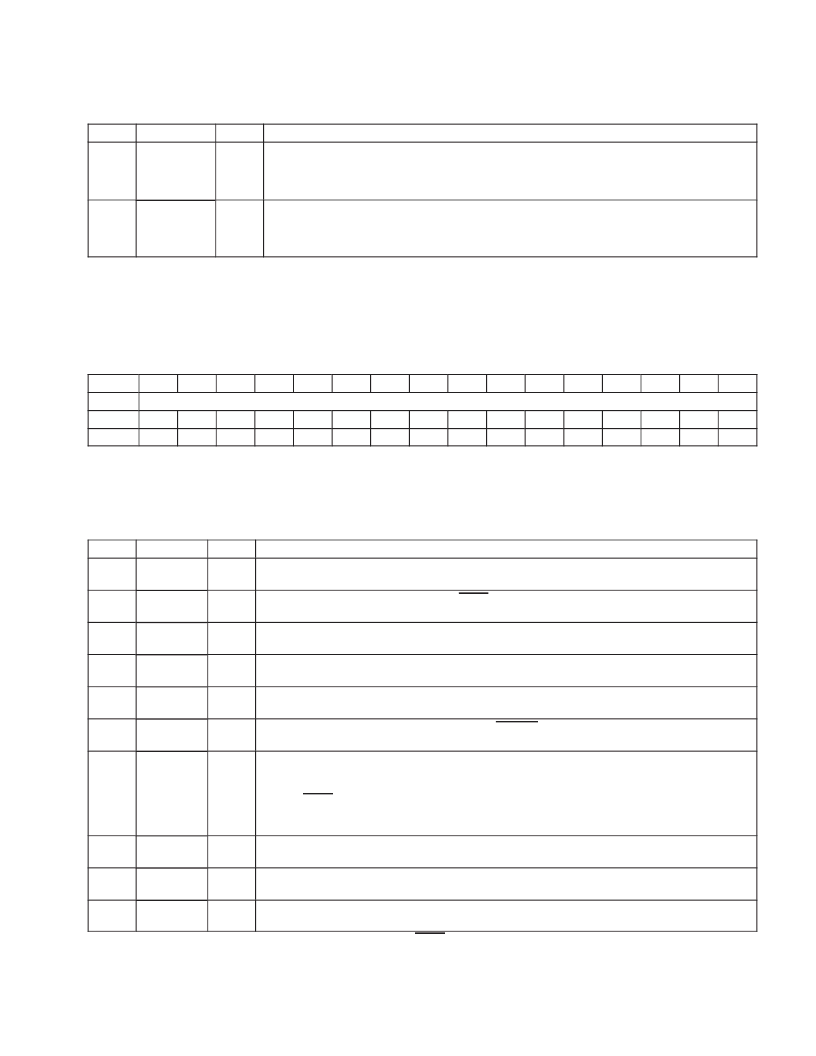

Table 43. Command Register Description (continued)

BIT

SIGNAL

TYPE

FUNCTION

1

MEM_EN

RW

Memory space enable. This bit controls whether or not the PCI6x21/PCI6x11 controller can claim cycles

in PCI memory space.

0 = Disables the PCI6x21/PCI6x11 response to memory space accesses (default)

1 = Enables the PCI6x21/PCI6x11 response to memory space accesses

0

IO_EN

RW

I/O space control. This bit controls whether or not the PCI6x21/PCI6x11 controller can claim cycles in PCI

I/O space.

0 = Disables the PCI6x21/PCI6x11 controller from responding to I/O space accesses (default)

1 = Enables the PCI6x21/PCI6x11 controller to respond to I/O space accesses

4.5

Status Register

The status register provides device information to the host system. Bits in this register can be read normally. A bit

in the status register is reset when a 1 is written to that bit location; a 0 written to a bit location has no effect. All bit

functions adhere to the definitions in the

PCI Bus Specification

, as seen in the bit descriptions. PCI bus status is shown

through each function. See Table 44 for a complete description of the register contents.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Status

Type

RW

RW

RW

RW

RW

R

R

RW

R

R

R

R

RU

R

R

R

Default

0

0

0

0

0

0

1

0

0

0

0

1

0

0

0

0

Register:

Offset:

Type:

Default:

Status

06h (Functions 0, 1)

Read-only, Read/Write

0210h

Table 44. Status Register Description

BIT

SIGNAL

TYPE

FUNCTION

15

PAR_ERR

RW

Detected parity error. This bit is set when a parity error is detected, either an address or data parity error.

Write a 1 to clear this bit.

14

SYS_ERR

RW

Signaled system error. This bit is set when SERR is enabled and the PCI6x21/PCI6x11 controller signaled

a system error to the host. Write a 1 to clear this bit.

13

MABORT

RW

Received master abort. This bit is set when a cycle initiated by the PCI6x21/PCI6x11 controller on the PCI

bus has been terminated by a master abort. Write a 1 to clear this bit.

12

TABT_REC

RW

Received target abort. This bit is set when a cycle initiated by the PCI6x21/PCI6x11 controller on the PCI

bus was terminated by a target abort. Write a 1 to clear this bit.

11

TABT_SIG

RW

Signaled target abort. This bit is set by the PCI6x21/PCI6x11 controller when it terminates a transaction on

the PCI bus with a target abort. Write a 1 to clear this bit.

109

PCI_SPEED

R

DEVSEL timing. These bits encode the timing of DEVSEL and are hardwired to 01b indicating that the

PCI6x21/PCI6x11 controller asserts this signal at a medium speed on nonconfiguration cycle accesses.

8

DATAPAR

RW

Data parity error detected. Write a 1 to clear this bit.

0 = The conditions for setting this bit have not been met.

1 = A data parity error occurred and the following conditions were met:

a. PERR was asserted by any PCI device including the PCI6x21/PCI6x11 controller.

b. The PCI6x21/PCI6x11 controller was the bus master during the data parity error.

c. The parity error response bit is set in the command register.

7

FBB_CAP

R

Fast back-to-back capable. The PCI6x21/PCI6x11 controller cannot accept fast back-to-back transactions;

thus, this bit is hardwired to 0.

6

UDF

R

UDF supported. The PCI6x21/PCI6x11 controller does not support user-definable features; therefore, this

bit is hardwired to 0.

5

66MHZ

R

66-MHz capable. The PCI6x21/PCI6x11 controller operates at a maximum PCLK frequency of 33 MHz;

therefore, this bit is hardwired to 0.

One or more bits in this register are cleared only by the assertion of GRST.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI6621 | DUAL/SINGLE SOCKET CARDBUS AND ULTRAMEDIA CONTROLLER |

| PCI6515 | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

| PCI6515GHK | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

| PCI6515ZHK | SINGLE SOCKET CARDBUS CONTROLLER WITH DEDICATED SMART CARD SOCKET |

| PCI7610LQFP | PC Card, UltraMedia, and Integrated 1394a-2000 OHCI Two-Port PHY/Link-Layer Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI6611GHK | 制造商:Texas Instruments 功能描述:DUAL/SGL SCKT CARDBUS AND ULTRAMEDIA CNTRLR W/ DEDICATED FLA - Trays |

| PCI6611ZHK | 制造商:Texas Instruments 功能描述:DUAL/SGL SCKT CARDBUS AND ULTRAMEDIA CNTRLR W/ DEDICATED FLA - Trays |

| PCI6612ZHK | 功能描述:外圍驅(qū)動器與原件 - PCI Integrated single socket RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI6620 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL SOCKET CARDBUS AND SMART CARD CONTROLLER WITH DEDICATED SD/MS-PRO SOCKETS |

| PCI6620GHK | 功能描述:外圍驅(qū)動器與原件 - PCI Integrated 2-Slot PC Card RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。