- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369952 > PCM3002EG 16/20-BIT SINGLE-ENDED ANALOG INPUT/OUTPUT STEREO AUDIO CODECS PDF資料下載

參數(shù)資料

| 型號: | PCM3002EG |

| 元件分類: | Codec |

| 英文描述: | 16/20-BIT SINGLE-ENDED ANALOG INPUT/OUTPUT STEREO AUDIO CODECS |

| 中文描述: | 16/20-BIT單端模擬輸入/輸出立體聲編解碼器 |

| 文件頁數(shù): | 29/39頁 |

| 文件大小: | 515K |

| 代理商: | PCM3002EG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

www.ti.com

PCM3002

PCM3003

SBAS079A–OCTOBER 2000–REVISED OCTOBER 2004

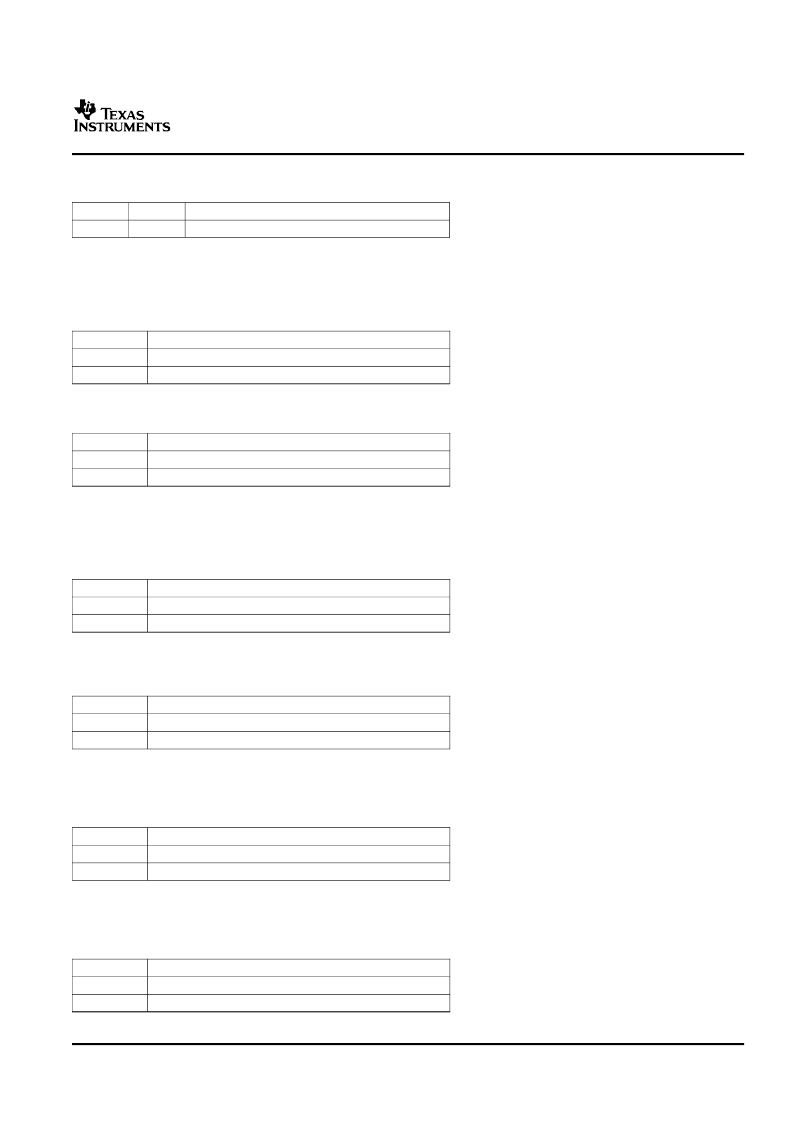

A[1:0]

Bits 10, 9: Register address

These bits define the address for register 2:

A1

1

A0

0

REGISTER

Register 2

PDAD:

Bit 8: ADC power-down control

This bit places the ADC section in the lowest power-consumption mode. The ADC operation is

stopped by cutting the supply current to the ADC section, and DOUT is fixed to zero during ADC

power-down mode enable. Figure 46 illustrates the ADC DOUT response for ADC power-down

ON/OFF. This does not affect the DAC operation.

PDAD

0

1

DAC POWER-DOWN STATUS

Power-down mode disabled (default)

Power-down mode enabled

BYPS:

Bit 7: ADC high-pass filter bypass control

This bit enables or disables the high-pass filter for the ADC.

BYPS

0

1

FILTER BYPASS STATUS

High-pass filter enabled (default)

High-pass filter disabled (bypassed)

PDDA:

Bit 6: DAC power-down control

This bit places the DAC section in the lowest power-consumption mode. The DAC operation is

stopped by cutting the supply current to the DAC section, and VOUT is fixed to GND during DAC

power-down mode enable. Figure 46 illustrates the DAC VOUT response for DAC power-down

ON/OFF. This does not affect the ADC operation.

PDDA

0

1

ADC POWER-DOWN STATUS

Power-down mode disabled (default)

Power-down mode enabled

ATC:

Bit 5: DAC attenuation data mode control

When set to 1, the register 0 attenuation data can be used for both DAC channels. In this case, the

register 1 attenuation data is ignored.

ATC

0

1

ATTENUATION CONTROL

Individual channel attenuation data control (default)

Common channel attenuation data control

IZD:

Bit 4: DAC infinite zero detection and mute control

This bit enables the infinite zero detection circuit in the PCM3002. When enabled, this circuit

disconnects the analog output amplifier from the delta-sigma DAC when the input is continuously

zero for 65,536 consecutive cycles of BCKIN.

IZD

0

1

INFINITE ZERO DETECT STATUS

Infinite zero detection and mute control disabled (default)

Infinite zero detection and mute control enabled

OUT:

Bit 3: DAC output enable control

When set to 1, the outputs are forced to V

/2 (bipolar zero). In this case, all registers in the

PCM3002 hold the present data. Therefore, when set to 0, the outputs return to the previous

programmed state.

OUT

0

1

DAC OUTPUT STATUS

DAC outputs enabled (default normal operation)

DAC outputs disabled (forced to BPZ)

29

相關PDF資料 |

PDF描述 |

|---|---|

| PCM3002EG4 | 16/20-BIT SINGLE-ENDED ANALOG INPUT/OUTPUT STEREO AUDIO CODECS |

| PCM3002EGE6 | 16/20-BIT SINGLE-ENDED ANALOG INPUT/OUTPUT STEREO AUDIO CODECS |

| PCM3003EG4 | 16/20-BIT SINGLE-ENDED ANALOG INPUT/OUTPUT STEREO AUDIO CODECS |

| PCM3060 | 24-BIT, 96/192-kHz ASYNCHRONOUS STEREO AUDIO CODEC |

| PCM3060PW | 24-BIT, 96/192-kHz ASYNCHRONOUS STEREO AUDIO CODEC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PCM3002EG/2K | 功能描述:接口—CODEC 16/20-Bit Sngl-end Anlg I/O Ster Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| PCM3002EG/2KE6 | 功能描述:接口—CODEC 16/20-Bit Sngl-end Anlg I/O Ster Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| PCM3002EG4 | 功能描述:接口—CODEC 16/20-Bit Sngl-end Anlg I/O Ster Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| PCM3002EGE6 | 功能描述:接口—CODEC 16/20-Bit Sngl-end Anlg I/O Ster Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| PCM3003 | 制造商:BB 制造商全稱:BB 功能描述:16-/20-Bit Single-Ended Analog Input/Output STEREO AUDIO CODECs |

發(fā)布緊急采購,3分鐘左右您將得到回復。