- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367899 > PE97632ES (Electronic Theatre Controls, Inc.) 3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications PDF資料下載

參數(shù)資料

| 型號: | PE97632ES |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 中文描述: | 3.2 GHz的Δ-Σ調(diào)制的低相位噪聲應(yīng)用分數(shù)N頻率合成器 |

| 文件頁數(shù): | 3/16頁 |

| 文件大?。?/td> | 373K |

| 代理商: | PE97632ES |

Advance Information

PE97632

Page 3 of 16

Document No. 70-0205-02

│

www.psemi.com

2006 Peregrine Semiconductor Corp. All rights reserved.

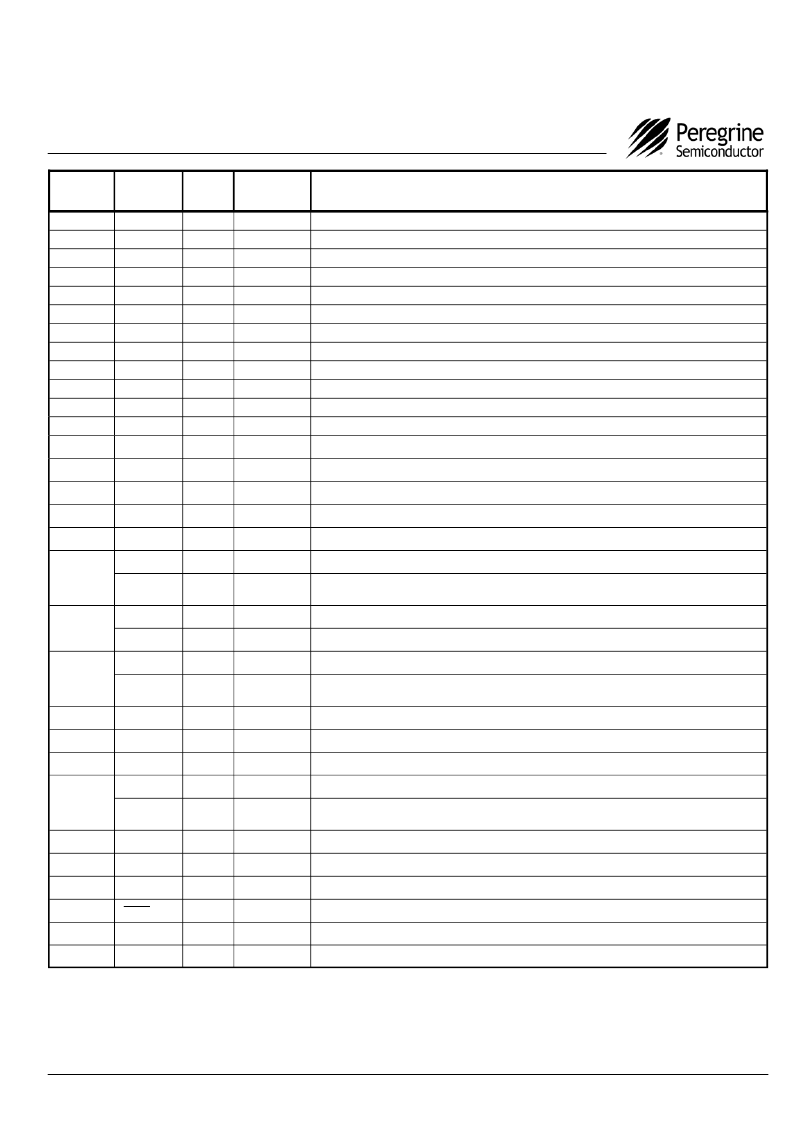

Pin No.

Pin

Name

K

7

K

8

K

9

K

10

K

11

K

12

K

13

K

14

K

15

K

16

K

17

V

DD

Valid

Mode

Direct

Direct

Direct

Direct

Direct

Direct

Direct

Direct

Direct

Direct

Direct

Type

Description

16

17

18

19

20

21

22

23

24

25

26

27

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

(Note 1)

K Counter bit7.

K Counter bit8.

K Counter bit9.

K Counter bit10.

K Counter bit11.

K Counter bit12.

K Counter bit13.

K Counter bit14.

K Counter bit15.

K Counter bit16.

K Counter bit17 (MSB).

Digital core V

DD

.

28

GND

Downbond

Ground

29

M

0

Direct

Input

M Counter bit0 (LSB).

30

M

1

Direct

Input

M Counter bit1.

31

M

2

Direct

Input

M Counter bit2

32

M

3

Direct

Input

M Counter bit3.

33

M

4

Direct

Input

M Counter bit4.

S_WR

Serial

Input

Serial load enable input. While S_WR is “l(fā)ow”, Sdata can be serially clocked. Primary register

data are transferred to the secondary register on S_WR or Hop_WR rising edge.

34

M

5

Direct

Input

M Counter bit5.

SDATA

Serial

Input

Binary serial data input. Input data entered MSB first.

35

M

6

Direct

Input

M Counter bit6.

SCLK

Serial

Input

Serial clock input. SDATA is clocked serially into the 20-bit primary register (E_WR “l(fā)ow”) or

the 8-bit enhancement register (E_WR “high”) on the rising edge of Sclk.

36

M

7

Direct

Input

M Counter bit7.

37

M

8

Direct

Input

M Counter bit8 (MSB).

38

A

0

Direct

Input

A Counter bit0 (LSB).

39

A

1

Direct

Input

A Counter bit1.

E_WR

Serial

Input

Enhancement register write enable. While E_WR is “high”, Sdata can be serially clocked into

the enhancement register on the rising edge of Sclk.

40

A

2

Direct

Input

A Counter bit2.

41

A

3

Direct

Input

A Counter bit3 (MSB).

42

DIRECT

Both

Input

Direct mode select. “High” enables direct mode. “Low” enables serial mode.

43

Pre_en

Direct

Input

Prescaler enable, active “l(fā)ow”. When “high”, Fin bypasses the prescaler.

44

V

DD

(Note 1)

Digital core V

DD

.

45

GND

Downbond

Ground

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PEB2030 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PEB2035-C | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PEB2040 | Telecom Switching Circuit |

| PEB2041N | Telecom Switching Circuit |

| PEB2041P | Telecom Switching Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PE9763EK | 制造商:PEREGRINE 制造商全稱:PEREGRINE 功能描述:3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| PE9763ES | 制造商:PEREGRINE 制造商全稱:PEREGRINE 功能描述:3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| PE9764 | 制造商:PASTERNACK 制造商全稱:Pasternack Enterprises, Inc. 功能描述:Precision 1.85mm Female to SSMA Male Adapter |

| PE9765 | 制造商:PASTERNACK 制造商全稱:Pasternack Enterprises, Inc. 功能描述:Precision 1.85mm Female to SSMA Female Adapter |

| PE9766 | 制造商:PASTERNACK 制造商全稱:Pasternack Enterprises, Inc. 功能描述:Precision 2.92mm Male to SSMA Female Adapter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。