- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367961 > PI6C102 (Pericom Semiconductor Corp.) Precision Clock Synthesizer for Mobile PCs PDF資料下載

參數(shù)資料

| 型號: | PI6C102 |

| 廠商: | Pericom Semiconductor Corp. |

| 英文描述: | Precision Clock Synthesizer for Mobile PCs |

| 中文描述: | 精密時鐘合成器移動PC |

| 文件頁數(shù): | 3/11頁 |

| 文件大小: | 588K |

| 代理商: | PI6C102 |

3

PS8164A 09/29/00

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

PI6C102

Precision Clock Synthesizer for Mobile PCs

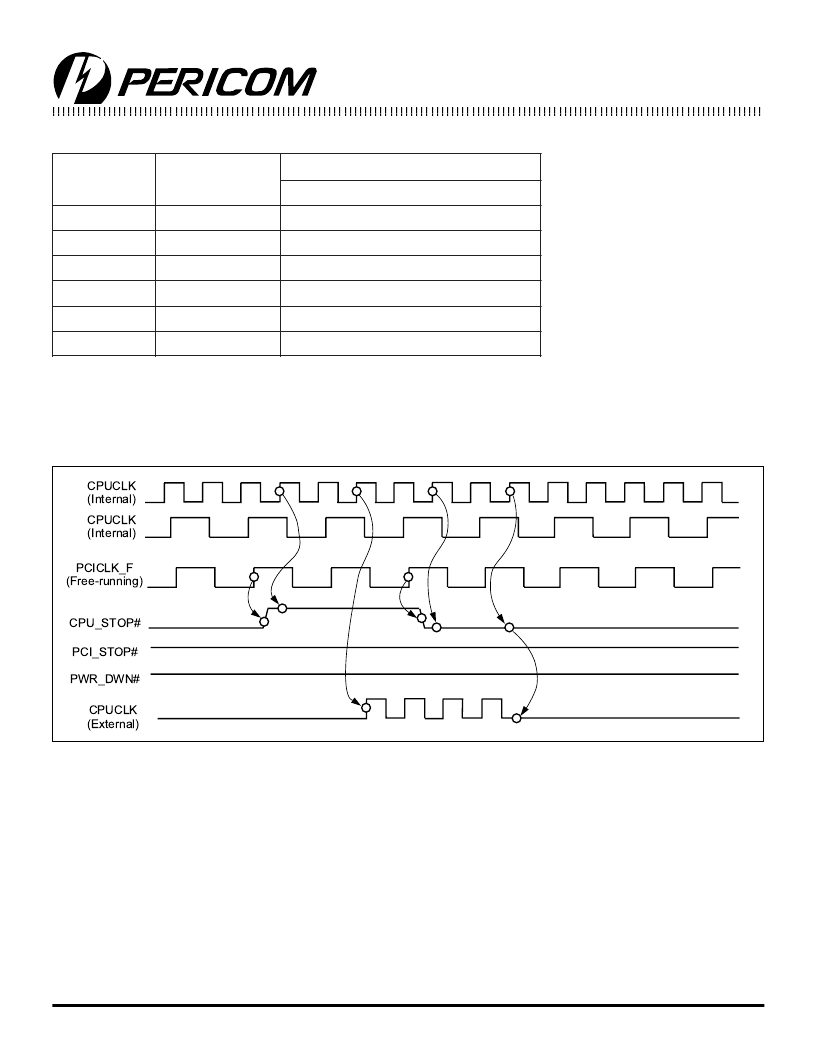

Power Management Timing

l

n

g

e

l

n

g

y

c

n

e

L

K

L

C

I

C

P

g

n

n

u

r

e

e

f

s

g

d

e

g

n

f

.

N

#

P

O

T

S

_

U

P

C

)

e

a

0

1

)

e

a

e

1

1

#

P

O

T

S

_

C

P

)

e

a

0

1

)

e

a

e

1

1

#

N

W

D

_

R

W

P

)

o

p

o

l

m

r

n

1

s

m

3

)

w

o

d

r

w

o

p

0

.

a

m

2

Notes:

1. Clock on/off latency is defined as the number of rising edges of free running PCICLKs

between when the clock disable goes low/high to when the first valid clock comes out of

the device.

2. Power-up latency is from when PWR_DWN# goes inactive (HIGH) to when the first valid

clocks are driven from the device.

CPU_STOP# is an input signal used to turn off the CPU clocks for

low power operation. CPU_STOP# is asserted asynchronously by

the external clock control logic with the rising edge of free running

PCI clock and is internally synchronized to the external PCICLK_F

output. All other clocks continue to run while the CPU clocks are

CPU_STOP# Timing Diagram

Notes:

1. All timing is referenced to the CPUCLK.

2. The Internal label means inside the chip and is a reference only.

3 CPU_STOP# is an input signal that must be made synchronous to the free running PCI_F.

4. ON/OFF latency shown in the diagram is 2 CPU clocks.

5. All other clocks continue to run undisturbed.

6. PWR_DWN# and PCI_STOP# are shown in a HIGH state.

7. Diagrams shown with respect to 66 MHz. Similar operation as CPU = 100 MHz.

disabled. The CPU clocks are always stopped in a LOW state and

started guaranteeing that the high pulse width is a full pulse. CPU

clock on latency is 2 or 3 CPU clocks and CPU clock off latency

is 2 or 3 CPU clocks.

CPUCLK

(Internal)

CPUCLK

(Internal)

PCICLK_F

(Free-running)

CPU_STOP#

PCI_STOP#

PWR_DWN#

CPUCLK

(External)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI6C102H | DIP Socket; No. of Contacts:16; Pitch Spacing:0.1"; Row Spacing:0.3"; Terminal Type:PCB; Leaded Process Compatible:Yes RoHS Compliant: Yes |

| PI6C104 | Spread Spectrum Clock Synthesizer for Desktop Pentium II |

| PI6C104H | Spread Spectrum Clock Synthesizer for Desktop Pentium II |

| PI6C104S | Spread Spectrum Clock Synthesizer for Desktop Pentium II |

| PI6C106 | Pentium/Pro System Clock Chip |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI6C102-16BH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU System Clock Generator |

| PI6C102-16DH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU System Clock Generator |

| PI6C102-16H | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU System Clock Generator |

| PI6C102H | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:Precision Clock Synthesizer for Mobile PCs |

| PI6C103 | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:Precision Clock Synthesizer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。