- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370013 > PowerPC 740 (IBM Microeletronics) 32-Bit Embedded Microprocessor(32位精簡(jiǎn)指令集嵌入式微處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | PowerPC 740 |

| 廠商: | IBM Microeletronics |

| 英文描述: | 32-Bit Embedded Microprocessor(32位精簡(jiǎn)指令集嵌入式微處理器) |

| 中文描述: | 32位嵌入式微處理器(32位精簡(jiǎn)指令集嵌入式微處理器) |

| 文件頁(yè)數(shù): | 14/48頁(yè) |

| 文件大?。?/td> | 608K |

| 代理商: | POWERPC 740 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

Page 14

Version 1.02

12/8/99

PowerPC 740 and PowerPC 750 Microprocessor

CMOS 0.20

μ

m Copper Technology, PID-8p, PPC740L and PPC750L, dd3.2

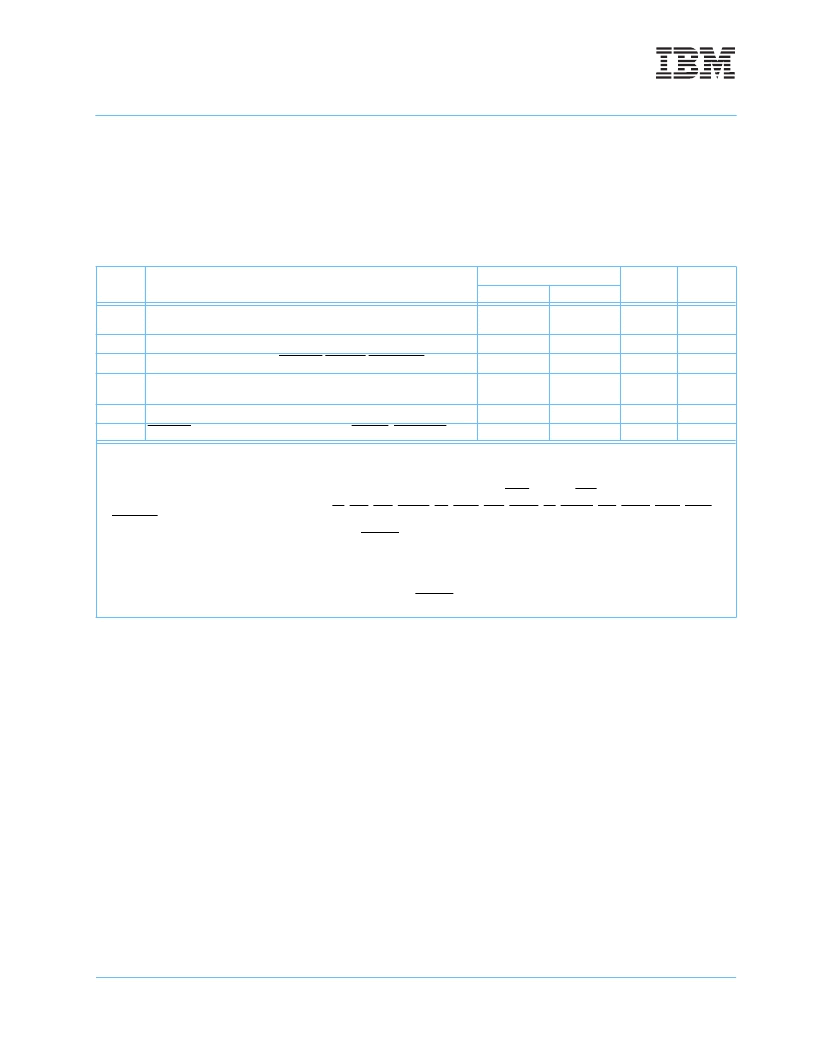

60x Bus Input AC Specifications

The following table provides the 60X bus input AC timing specifications for the 750 as defined in Figure 3 and

Figure 4. Input timing specifications for the L2 bus are provided in Section, “L2 Bus Input AC Specifications”

on page 20.

60X Bus Input Timing Specifications

1

See Table “Recommended Operating Conditions,” on page 9, for operating conditions.

Num

Characteristic

All Frequencies

Unit

Notes

Minimum

Maximum

10a

Address/Data/Transfer Attribute Inputs Valid to SYSCLK (Input

Setup)

2.5

—

ns

2

10b

All Other Inputs Valid to SYSCLK (Input Setup)

2.5

—

ns

3

10c

Mode Select Input Setup to HRESET (DRTRY,TLBISYNC)

8

—

t

sysclk

4,5,6,7

11a

SYSCLK to Address/Data/Transfer Attribute Inputs Invalid (Input

Hold)

0.6

—

ns

2

11b

SYSCLK to All Other Inputs Invalid (Input Hold)

0.6

—

ns

3

11c

HRESET to mode select input hold (DRTRY, TLBISYNC)

0

—

ns

4,6,7

Note:

1. Input specifications are measured from the Vm of the signal in question to the Vm of the rising edge of the input SYSCLK. Input and output timings are

measured at the pin (see Figure 3

2. Address/Data Transfer Attribute inputs are composed of the following–A[0:31], AP[0:3], TT[0:4],TBST, TSIZ[0:2], GBL, DH[0:31], DL[0:31], DP[0:7].

3. All other signal inputs are composed of the following–TS, ABB, DBB, ARTRY, BG, AACK, DBG, DBWO, TA, DRTRY, TEA, DBDIS, TBEN, QACK,

TLBISYNC.

4. The setup and hold time is with respect to the rising edge of HRESET (see Figure 4).

5. t

, is the period of the external clock (SYSCLK) in nanoseconds (ns). The numbers given in the table must be multiplied by the period of SYSCLK

to compute the actual time duration (in ns) of the parameter in question.

6. These values are guaranteed by design, and are not tested.

7. This specification is for configuration mode select only. Also note that the HRESET must be held asserted for a

minimum of 255 bus clocks

after the

PLL re-lock time during the power-on reset sequence.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PowerPC 750CX | 32-Bit Reduced Instruction Set Computer (RISC) Microprocessors(32位精簡(jiǎn)指令集微處理器) |

| PowerPC 750 | 32-Bit Embedded Microprocessor(32位精簡(jiǎn)指令集嵌入式微處理器) |

| PP-MOD1V2 | ISP INTERFACE MODULE |

| PP01002 | GEHOERSCHUTZ OHRSTOEPSEL 250ST Inhalt pro Packung: 250 Stk. |

| PP0901SA | Direct ProTek Replacement:PP0901SA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| POWERPLUG15W | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:AC/DC POWER SUPPLY |

| POWERPLUG24W | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:AC/DC POWER SUPPLY |

| POWERPLUS 2C 2500MAH | 制造商:Energizer Battery Company 功能描述: |

| POWERPLUS 2D 2500MAH | 制造商:Energizer Battery Company 功能描述: |

| POWERPLUS 4AAA 850MAH | 制造商:Energizer Battery Company 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。