- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368095 > PPC405EX-SpAfffTx (Applied Micro Circuits Corp.) PowerPC 405EX Embedded Processor PDF資料下載

參數(shù)資料

| 型號(hào): | PPC405EX-SpAfffTx |

| 廠商: | Applied Micro Circuits Corp. |

| 英文描述: | PowerPC 405EX Embedded Processor |

| 中文描述: | 嵌入式處理器的PowerPC 405EX |

| 文件頁數(shù): | 42/67頁 |

| 文件大小: | 457K |

| 代理商: | PPC405EX-SPAFFFTX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當(dāng)前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

PPC405EX – PowerPC 405EX Embedded Processor

42

AMCC Proprietary

Revision 1.09 - August 21, 2007

Preliminary Data Sheet

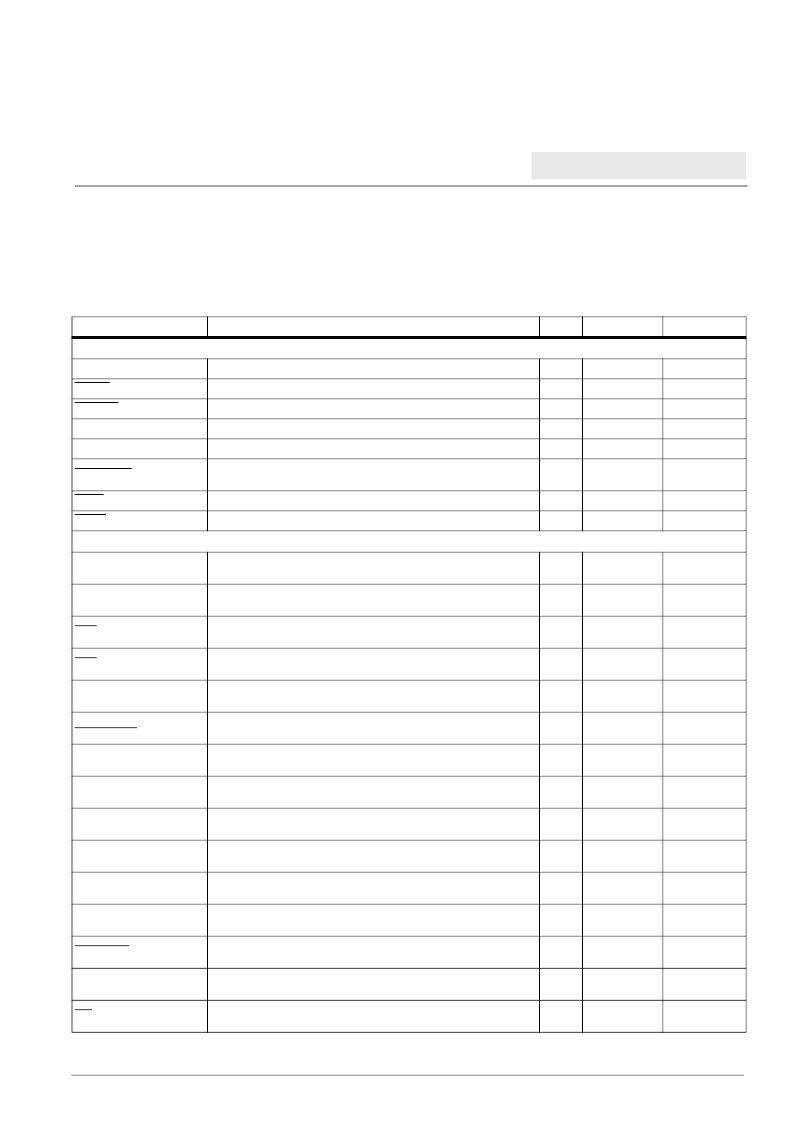

NAND Flash Interface

NFALE

Address latch enable.

I/O

3.3V LVTTL

NFCE0

Chip select 0.

O

3.3V LVTTL

NFCE1:3

Chip selects 1:3.

I/O

3.3V LVTTL

1, 2

NFCLE

Command latch enable.

I/O

3.3V LVTTL

NFData00:15

Data Bus

I/O

3.3V LVTTL

NFRdyBusy

Read/Busy. If low, indicates that Read/Erase command is in process.

If high, indicates that the command is complete.

I/O

3.3V LVTTL

NFRE

Read enable.

I/O

3.3V LVTTL

NFWE

Write enable.

I/O

3.3V LVTTL

DDR1/2 SDRAM Interface

MemData00:31

Memory data.

I/O

2.5V (1.8V)

SSTL2 Dr/Rcv

MemAddr00:14

Memory address.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

RAS

Row address strobe.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

CAS

Column address strobe.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

MemClkEn

Clock enable.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

MemClkOut0

MemClkOut0

Differential DDR SDRAM clock output.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

MemFBD

Feedback driver.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

MemFBR

Feedback receiver. Connect externally to MemFBD.

I

2.5V (1.8V)

SSTL2 Dr/Rcv

MemODT0:1

On-die termination.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

DM0:4

Write data byte lane mask. DM4 is the byte lane mask for the ECC

byte lane.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

DQS0:4

Byte lane strobe. DQS4 is the strobe for the ECC lane.

I/O

2.5V (1.8V)

SSTL2 Dr/Rcv

BA0:2

Bank address for up to eight banks.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

BankSel0:1

Bank select for up to two SDRAM memory banks.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

ECC0:7

ECC check bit byte.

I/O

2.5V (1.8V)

SSTL2 Dr/Rcv

WE

Write enable.

O

2.5V (1.8V)

SSTL2 Dr/Rcv

Table 6. Signal Functional Description (Sheet 5 of 7)

Notes:

1. Receiver input has hysteresis.

2. Must pull up. See “Pull-Up and Pull-Down Resistors” on page 37 for recommended termination values.

3. Must pull down. See “Pull-Up and Pull-Down Resistors” on page 37 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

Signal Name

Description

I/O

Type

Notes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC405EZ-CSAfffTx | PowerPC 405EZ Embedded Processor |

| PPC405GP-3BE133C | Power PC 405GP Embedded Processor |

| PPC405GP-3KE133C | Power PC 405GP Embedded Processor |

| PPC405GP-3KE133CZ | Power PC 405GP Embedded Processor |

| PPC405GP-3KE200C | Power PC 405GP Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC405EX-SPD400T | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 600 MHZ, 2 PCIE, 2 10/100/1G ETHE - Trays |

| PPC405EX-SPD533T | 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 600 MHZ, 2 PCIE, 2 10/100/1G ETHE - Trays |

| PPC405EX-SPD600T | 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 600 MHZ, 2 PCIE, 2 10/100/1G ETHE - Trays |

| PPC405EX-SSA333T | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 533 MHZ, 2 PCIE, 2 10/100/1G ETHE - Trays |

| PPC405EX-SSA400T | 制造商:AMCC 功能描述:32 BIT POWERPC CORE, UP TO 533 MHZ, 2 PCIE, 2 10/100/1G ETHE - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。