- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄297244 > RHF1401KSO-01V (STMICROELECTRONICS) 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO48 PDF資料下載

參數(shù)資料

| 型號: | RHF1401KSO-01V |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | ADC |

| 英文描述: | 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO48 |

| 封裝: | HERMETIC SEALED, SOP-48 |

| 文件頁數(shù): | 33/34頁 |

| 文件大小: | 1474K |

| 代理商: | RHF1401KSO-01V |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當前第33頁第34頁

Timing characteristics

RHF1401

8/34

Doc ID 13317 Rev 5

5

Timing characteristics

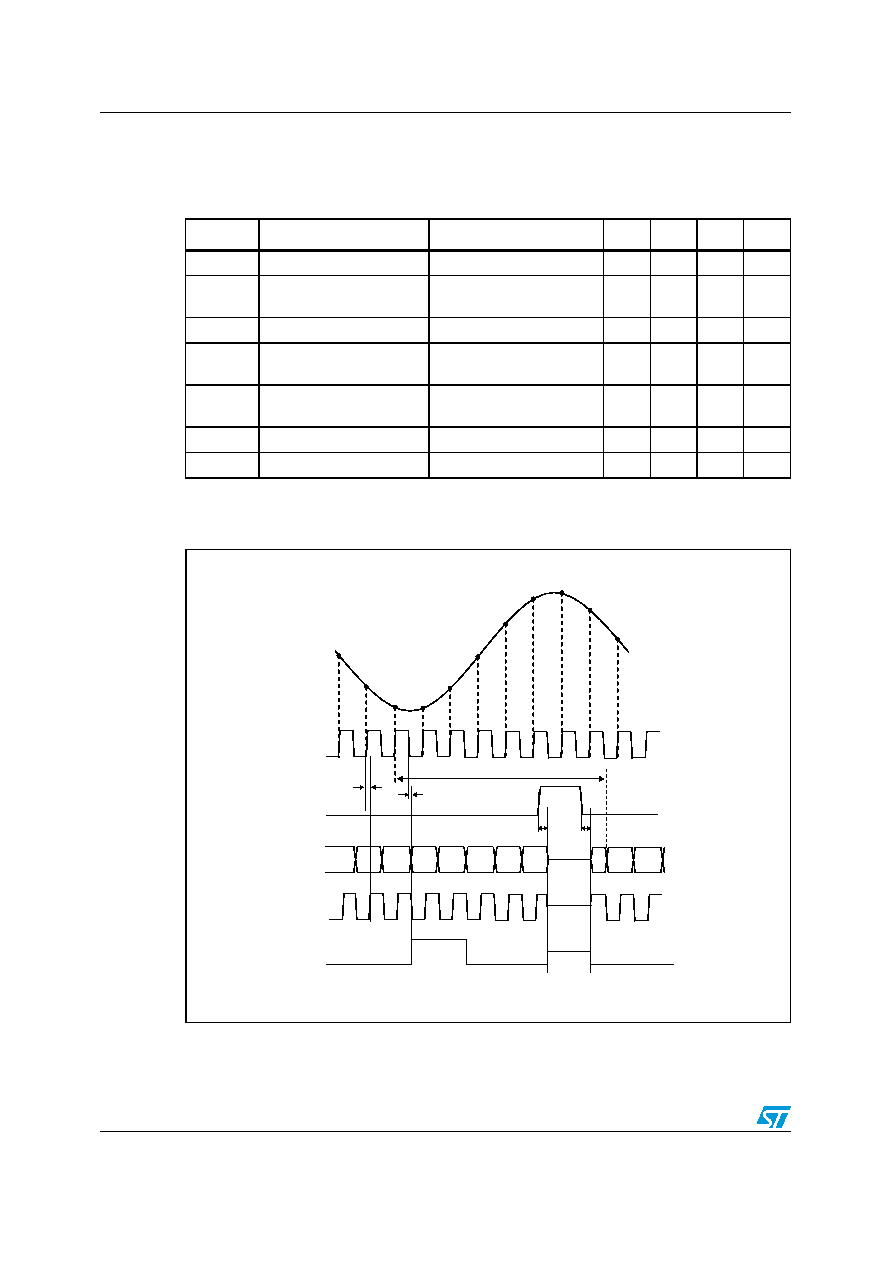

Figure 11.

Timing diagram

The input signal is sampled on the rising edge of the clock while the digital outputs are

synchronized on the falling edge of the clock. The duty cycles on DR and CLK are the same.

Table 2.

Timing characteristics

Symbol

Parameter

Test conditions

Min

Typ

Max

Unit

DC

Clock duty cycle

Fs = 20 Msps

45

50

65

%

Tod

Data output delay (fall of

clock to data valid) (1)

1.

As per Figure 11.

10 pF load capacitance

5

7.5

13

ns

Tpd

Data pipeline delay(2)

2.

If the duty cycle does not equal 50%: Tpd = 7 cycles + CLK pulse width.

Duty cycle = 50%

7.5

cycles

Ton

Falling edge of OEB to

digital output valid data

1ns

Toff

Rising edge of OEB to

digital output tri-state

1ns

TrD

Data rising time

10 pF load capacitance

6

ns

TfD

Data falling time

10 pF load capacitance

3

ns

N-2

N-1

N

N+1

N+2

N+3

N+4

N+5

N+6

N+7

N+8

N-8

N-7

N -6

N

N-5

N -4

N+1

N-3

N-1

HZ state

Analog

input

CLK

OEB

Data

output

DR

Toff

Ton

Tpd +Tod

Tod

AM06120

OR

Tod

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RHRXH162373K2 | ALVC/VCX/A SERIES, DUAL 8-BIT DRIVER, TRUE OUTPUT, CDFP48 |

| RJ11-6LCT | TELECOM AND DATACOM CONNECTOR, JACK |

| RKS1500DKK | Silicon Epitaxial Planar Diode for UHF/VHF tuner Band Switch |

| RL1024KAQ-011 | SPECIALTY ANALOG CIRCUIT, CDIP22 |

| RLN | RLN/RLS Class H Fuses |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RHF1401KSO1 | 制造商:STMicroelectronics 功能描述:ADC SGL PIPELINED 20MSPS 14BIT PARALLEL 48SOIC - Bulk |

| RHF1401KSO2 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Rad-hard 14-bit 20Msps 85mW A/D converter |

| RHF310 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Rad-hard 400 ??A high-speed operational amplifier |

| RHF310K-01V | 制造商:STMicroelectronics 功能描述: |

| RHF310K1 | 制造商:STMicroelectronics 功能描述:RAD-HARD 400 µA HIGH-SPEED OPERATIONAL AMPLIFIER (EM) - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。