- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄192305 > S71GL064A04BFI0B2 (Spansion Inc.) Stacked Multi-Chip Product (MCP) Flash Memory and RAM PDF資料下載

參數(shù)資料

| 型號(hào): | S71GL064A04BFI0B2 |

| 廠商: | Spansion Inc. |

| 英文描述: | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| 中文描述: | 堆疊式多芯片產(chǎn)品(MCP)的閃存和RAM |

| 文件頁數(shù): | 86/102頁 |

| 文件大小: | 1606K |

| 代理商: | S71GL064A04BFI0B2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁當(dāng)前第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

84

S71GL032A Based MCPs

S71GL032A_00_A0 March 31, 2005

Advance

Info rmation

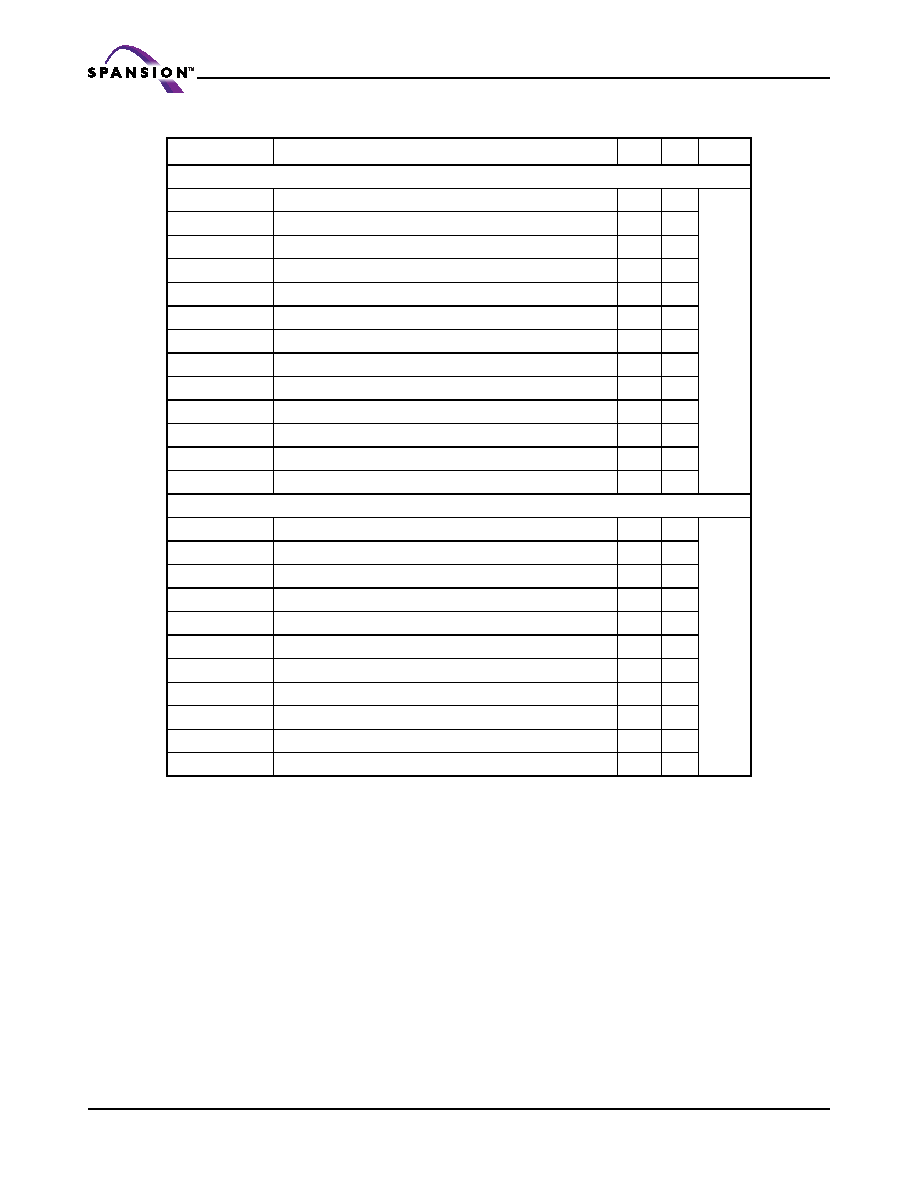

Table 26. Switching Characteristics

Notes:

1. Test conditions assume signal transition time of 1V/ns or higher, timing reference levels of VCC(typ.) /2, input pulse levels of

0 to VCC(typ.), and output loading of the specified IOL/IOH and 30 pF load capacitance.

2. tHZOE, tHZCE, tHZBE and tHZWE transitions are measured when the outputs enter a high-impedance state.

3. High-Z and Low-Z parameters are characterized and are not 100% tested.

4. To achieve 55-ns performance, the read access should be CE# controlled. In this case tACE is the critical parameter and tSK is

satisfied when the addresses are stable prior to chip enable going active. For the 70-ns cycle, the addresses must be stable

within 10 ns after the start of the read cycle.

5. The internal write time of the memory is defined by the overlap of WE#, CE#1 = VIL, CE2 = VIH, BHE and/or BLE =VIL. All

signals must be Active to initiate a write and any of these signals can terminate a write by going Inactive. The data input set-

up and hold timing should be referenced to the edge of the signal that terminates write.

Parameter

Description

Min

Max

Unit

Read Cycle

tRC

Read Cycle Time

70

ns

tAA

Address to Data Valid

70

tOHA

Data Hold from Address Change

10

tACE

CE#1 Low and CE2 High to Data Valid

70

tDOE

OE# Low to Data Valid

35

tLZOE

OE# Low to Low Z (note 2, 3)

5

tHZOE

OE# High to High Z (note 2, 3)

25

tLZCE

CE#1 Low and CE2 High to Low Z (note 2, 3)

5

tHZCE

CE#1 High and CE2 Low to High Z (note 2, 3)

25

tDBE

BHE# / BLE# Low to Data Valid

70

tLZBE

BHE# / BLE# Low to Low Z (note 2, 3)

5

tHZBE

BHE# / BLE# High to High Z (note 2, 3)

25

tSK (note 4)

Address Skew

10

Write Cycle (note 5)

tWC

Write Cycle Time

70

ns

tSCE

CE#1 Low an CE2 High to Write End

55

tAW

Address Set-Up to Write End

55

tHA

Address Hold from Write End

0

tSA

Address Set-Up to Write Start

0

tPWE

WE# Pulse Width

55

tBW

BLE# / BHE# LOW to Write End

55

tSD

Data Set-up to Write End

25

tHD

Data Hold from Write End

0

tHZWE

WE# Low to High Z (note 2, 3)

25

tLZWE

WE# High to Low Z (note 2, 3)

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S71GL064A04BFI0B3 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFI0F3 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFI0F2 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFW0B2 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFW0B3 | Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S71GL064A04BFI0B3 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFI0F0 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFI0F2 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFI0F3 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

| S71GL064A04BFW0B0 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Product (MCP) Flash Memory and RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。