- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372122 > SC16C752IB48 (NXP Semiconductors N.V.) Dual UART with 64-byte FIFO PDF資料下載

參數(shù)資料

| 型號(hào): | SC16C752IB48 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 收發(fā)器 |

| 英文描述: | Dual UART with 64-byte FIFO |

| 封裝: | SC16C752IB48<SOT313-2 (LQFP48)|<<http://www.nxp.com/packages/SOT313-2.html<1<week 17, 2005,; |

| 文件頁(yè)數(shù): | 24/47頁(yè) |

| 文件大?。?/td> | 604K |

| 代理商: | SC16C752IB48 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

Philips Semiconductors

SC16C752

Dual UART with 64-byte FIFO

Product data

Rev. 04 — 20 June 2003

24 of 47

9397 750 11635

Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Remark:

The three error bits (parity, framing, break) may not be updated correctly in

the first read of the LSR when the input clock (XTAL1) is running faster than 36 MHz.

However, the second read is always correct. It is strongly recommended that when

using this device with a clock faster than 36 MHz, that the LSR be read twice and only

the second read be used for decision making. All other bits in the LSR are correct on

all reads.

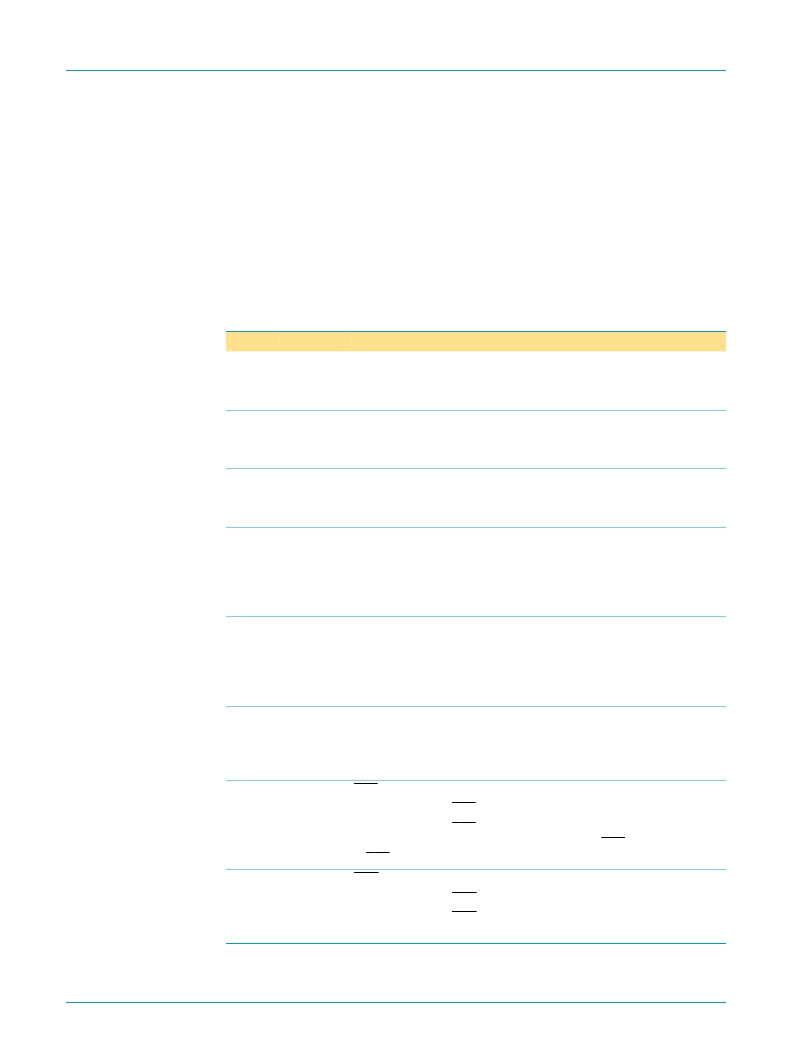

7.6 Modem control register (MCR)

The MCR controls the interface with the mode, data set, or peripheral device that is

emulating the modem.

Table 14

shows modem control register bit settings.

[1]

MCR[7:5] can only be modified when EFR[4] is set, i.e., EFR[4] is a write enable.

Table 14:

Bit

7

Modem Control Register bits description

Symbol

Description

MCR[7]

[1]

Clock select.

Logic 0 = Divide-by-1 clock input.

Logic 1 = Divide-by-4 clock input.

MCR[6]

[1]

TCR and TLR enable.

Logic 0 = no action.

Logic 1 = Enable access to the TCR and TLR registers.

MCR[5]

[1]

Xon Any.

Logic 0 = Disable Xon Any function.

Logic 1 = Enable Xon Any function.

MCR[4]

Enable loop-back.

Logic 0 = Normal operating mode.

Logic 1 = Enable local loop-back mode (internal). In this mode the

MCR[3:0] signals are looped back into MSR[7:4] and the TX output

is looped back to the RX input internally.

MCR[3]

IRQ enable OP.

Logic 0 = Forces INTA-INTB outputs to the 3-State mode and OP

output to HIGH state.

Logic 1 = Forces the INTA-INTB outputs to the active state and OP

output to LOW state. In loop-back mode, controls MSR[7].

MCR[2]

FIFO Ready enable.

Logic 0 = Disable the FIFO Rdy register.

Logic 1 = Enable the FIFO Rdy register.

In loop-back mode, controls MSR[6].

MCR[1]

RTS

Logic 0 = Force RTS output to inactive (HIGH).

Logic 1 = Force RTS output to active (LOW).

In loop-back mode, controls MSR[4]. If Auto-RTS is enabled, the

RTS output is controlled by hardware flow control.

MCR[0]

DTR

Logic 0 = Force DTR output to inactive (HIGH).

Logic 1 = Force DTR output to active (LOW).

In loop-back mode, controls MSR[5].

6

5

4

3

2

1

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SC16C754 | Quad UART with 64-byte FIFO |

| SC16C754IA68 | Quad UART with 64-byte FIFO |

| SC16C754IB80 | Quad UART with 64-byte FIFO |

| SC2000 | Universal Timeslot Interchange |

| SC2001G-10 | Bus Exchanger |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC16C752IB48,128 | 功能描述:UART 接口集成電路 Dual UART 64-byte FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C752IB48,151 | 功能描述:UART 接口集成電路 16C 2.5V-5V 2CH UART 64B FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C752IB48,157 | 功能描述:UART 接口集成電路 16C 2.5V-5V 2CH UART 64B FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C754 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Quad UART with 64-byte FIFO |

| SC16C754B | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:5 V, 3.3 V and 2.5 V quad UART, 5 Mbit/s (max.) with 64-byte FIFOs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。