- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376341 > SCM69C433 (Motorola, Inc.) A Flexible Content-Addressable Memory (16K x 64 CAM)(1M內(nèi)容可尋址存儲(chǔ)器) PDF資料下載

參數(shù)資料

| 型號(hào): | SCM69C433 |

| 廠商: | Motorola, Inc. |

| 英文描述: | A Flexible Content-Addressable Memory (16K x 64 CAM)(1M內(nèi)容可尋址存儲(chǔ)器) |

| 中文描述: | 一個(gè)靈活的內(nèi)容尋址存儲(chǔ)器(16K的× 64 CAM)的(100萬(wàn)內(nèi)容可尋址存儲(chǔ)器) |

| 文件頁(yè)數(shù): | 8/22頁(yè) |

| 文件大小: | 167K |

| 代理商: | SCM69C433 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

MCM69C433

SCM69C433

8

MOTOROLA FAST SRAM

INTERRUPT BIT DEFINITIONS

Bit 0:

1 = Enable interrupt on insert with full entry

queue

1 = Enable interrupt on insert with full table

1 = Enable interrupt on completion of

CHECK–FOR–VALUE instruction

1 = Enable interrupt on completion of

INITIALIZE–TABLE instruction

1 = Enable interrupt on failed attempt to enter

fast–entry mode

1 = Enable interrupt on CAM table reaching

almost–full point

1 = Enable interrupt on fast read with non–empty

queue

1 = Enable interrupt on illegal instruction

Bit 1:

Bit 2:

Bit 3:

Bit 4:

Bit 5:

Bit 6:

Bit 7:

INSTRUCTION SET DETAILS

The MCM69C433 is prepared for match operations by

writing to data and instruction registers via the control port. In

the general case, required data is loaded into I/O registers

0 – 3, then an instruction is issued by writing an operation

code to the instruction register. As a result of running an

instruction, the CAM table can be modified, bit(s) can be set

in the flag register, error codes can be returned in the error

code register, and an interrupt can be generated if enabled.

For a particular condition to generate an interrupt, the inter-

rupt register bit specific to that condition must be set. The

user should verify that the operation–complete bit of the flag

register is set before executing the next instruction, if the

instruction just executed modifies I/O registers.

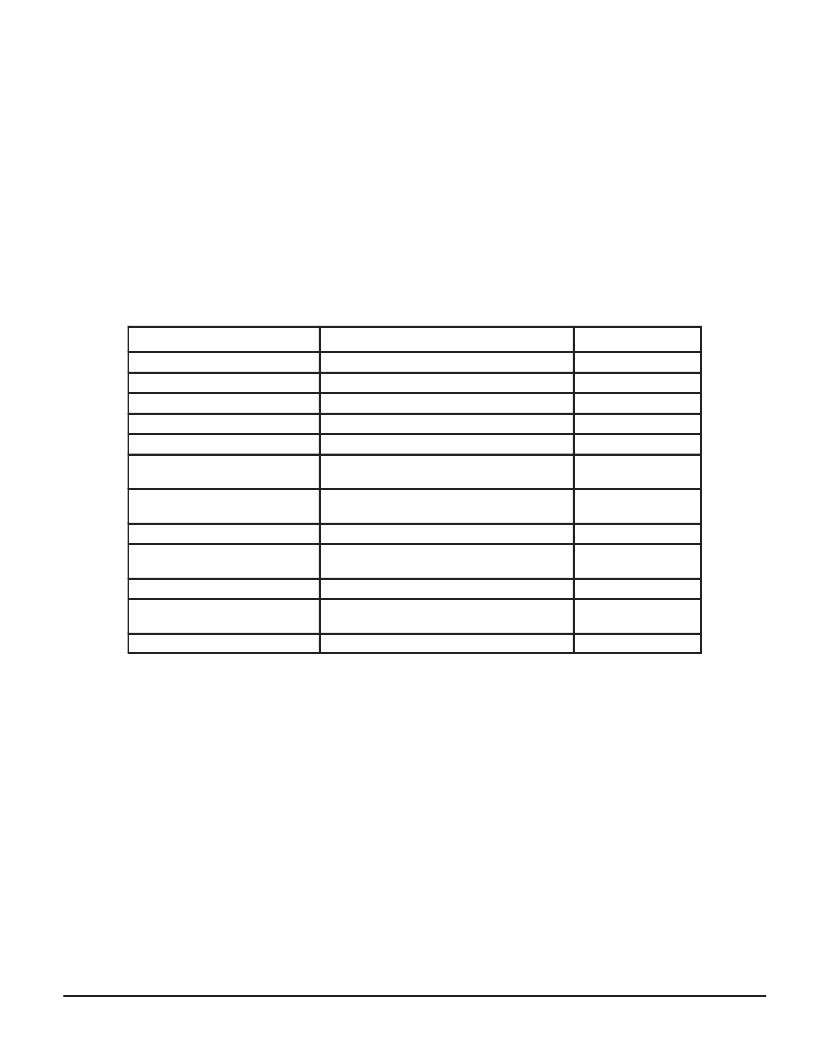

Table 1. MCM69C433 Operation Summary

Operation

Description

OP Code (Base 16)

INSERT VALUE

Loads a new entry into the CAM table

0000 or 000F

DELETE VALUE

Removes an entry from the CAM table

0001 or 000E

CHECK FOR VALUE

Runs a match cycle via the control port

0006

INITIALIZE TABLE

Prepares CAM table for matching

000B

FAST–ENTRY MODE

Selects entry mode suited for initial CAM table load

0004

BUFFERED–ENTRY MODE

Selects entry mode suited for simultaneous loading

and matching

0005

SET ATM MODE

Enter mode that provides concurrent VPC/VCC

search

0008

RETURN ENTRY COUNT

Determines number of entries in CAM

0003

SET GLOBAL–MASK REGISTER

Determines match bits to be checked in a match

operation

0002 or 000D

SET ALMOST–FULL POINT

Defines CAM almost–full condition

0007

SET FAST–READ REGISTER

Defines table entry that is output by the fast–read

operation

0009

FAST READ

Outputs one CAM table entry

000A

INSERT VALUE

This instruction is used to load a new match/output value

into the CAM. The contents of I/O registers 0 – 3 are con-

catenated, with bit 15 of register 3 as the most significant bit,

and bit 0 of register 0 as the least significant bit.

If the MCM69C433 is running in the buffered–entry mode,

the resulting 64–bit value is written to the first available loca-

tion in the entry queue, and is immediately available for

matching. If a buffered insert–value instruction is attempted

when the entry queue is full (indicated by bit 5 of the flag reg-

ister = 1), no value is written, an error code of FFF816 is re-

turned in the error code register, and the error–condition flag

(bit 7) is set in the flag register. An interrupt is generated, if

enabled by bit 0 of the interrupt register being set.

If the MCM69C433 is running in the fast–entry mode, the

concatenated 64–bit value is written directly to the CAM

array. If an insert–value instruction is attempted when in

fast–entry mode and the table is full, no value is written, an

error code of FFF916 is returned in the error code register,

and the error–condition flag (bit 7) is set in the flag register.

(The table–full condition is indicated by bit 6 of the flag regis-

ter being set.) An interrupt is generated, if enabled by bit 1 of

the interrupt register being set.

Only one entry is allowed for a given match pattern. If an

entry is made in the table that duplicates an existing match

pattern, it will overwrite the entry already in the CAM table, if

the CAM is in buffered–entry mode. The user must ensure

that no entries with the same match pattern are inserted in

fast–entry mode.

DELETE VALUE

This instruction is used to remove a match/output value

from the CAM. The contents of I/O registers 0 – 3 are con-

catenated, with bit 15 of register 3 as the most significant bit,

and bit 0 of register 0 as the least significant bit. The bits that

have a 0 in the corresponding bit of the global–mask register

are used to find a matching entry in the CAM table. If such an

entry is found, it is invalidated. Note that any bit that is not a

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SD1012-03 | Side Door Adapter |

| SD1013-03 | RF MICROWAVE TRANSISTORS 108-152 MHZ APPLICATIONS |

| SD1013-3 | RF & MICROWAVE TRANSISTORS 108-152 MHz APPLICATIONS |

| SD1014-02 | PTSE 8C 8#20 PIN RECP |

| SD1014 | RF & MICROWAVE TRANSISTORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCM69C433TQ15 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16K x 64 CAM |

| SCM69C433TQ15R | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16K x 64 CAM |

| SCM8245ALVV400D | 制造商:Freescale Semiconductor 功能描述:INTEGEATED HOST PROC |

| SCM8245ALZU400D | 制造商:Freescale Semiconductor 功能描述:INTEGRATED HOST PROC |

| SCM9B-3000 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Computer-to-Analog Output Modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。