- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376409 > SN74LS165N (MOTOROLA INC) One-Chip USB LED-based Navigation Sensor PDF資料下載

參數(shù)資料

| 型號(hào): | SN74LS165N |

| 廠商: | MOTOROLA INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | One-Chip USB LED-based Navigation Sensor |

| 中文描述: | LS SERIES, 8-BIT RIGHT PARALLEL IN SERIAL OUT SHIFT REGISTER, COMPLEMENTARY OUTPUT, PDIP16 |

| 封裝: | PLASTIC, DIP-16 |

| 文件頁數(shù): | 2/6頁 |

| 文件大小: | 157K |

| 代理商: | SN74LS165N |

*For the LS162A and

*

LS163A only.

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

5-279

FAST AND LS TTL DATA

SN54/74LS160A

SN54/74LS161A

SN54/74LS162A

SN54/74LS163A

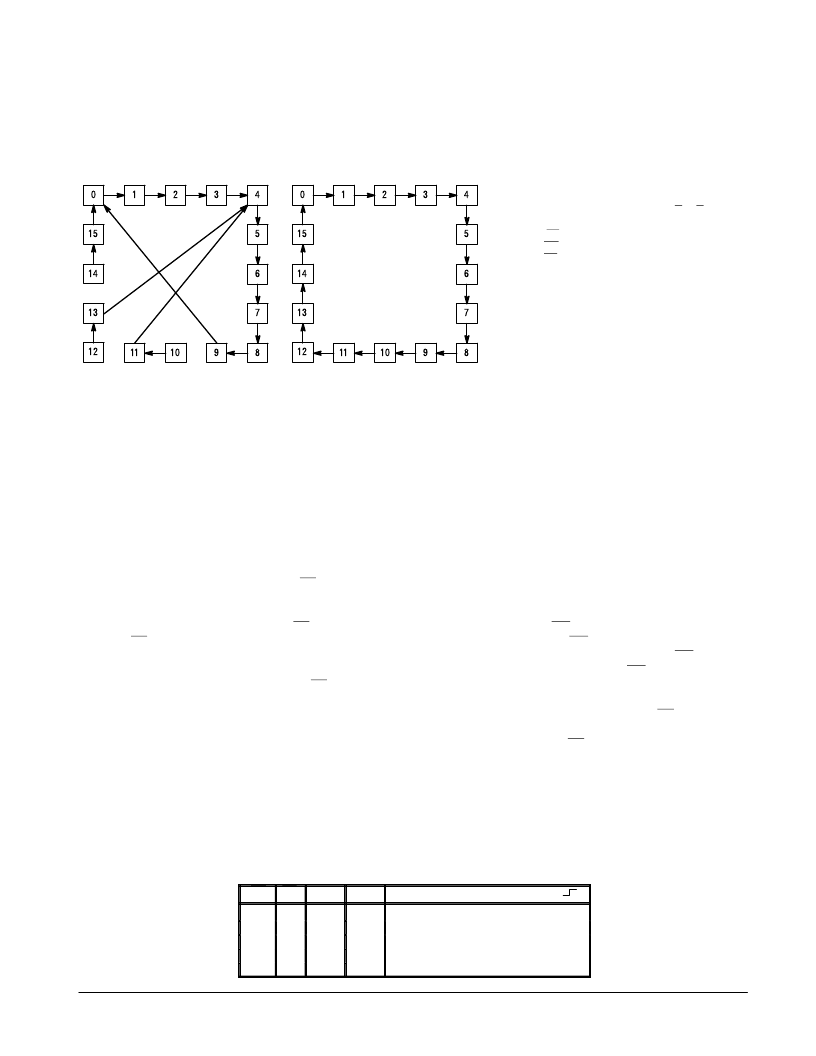

STATE DIAGRAM

LS160A

LS162A

LS161A

LS163A

NOTE:

The LS160A and LS162A can be preset to any state,

but will not count beyond 9. If preset to state 10, 11,

12, 13, 14, or 15, it will return to its normal sequence

within two clock pulses.

LOGIC EQUATIONS

Count Enable = CEP

CET

PE

TC for LS160A & LS162A = CET

Q0

Q1

Q2

Q3

TC for LS161A & LS163A = CET

Q0

Q1

Q2

Q3

Preset = PE

CP + (rising clock edge)

Reset = MR (LS160A & LS161A)

Reset = SR

CP + (rising clock edge)

Reset =

(LS162A & LS163A)

FUNCTIONAL DESCRIPTION

The LS160A/161A/162A/163A are 4-bit synchronous

counters with a synchronous Parallel Enable (Load) feature.

The counters consist of four edge-triggered D flip-flops with

the appropriate data routing networks feeding the D inputs. All

changes of the Q outputs (except due to the asynchronous

Master Reset in the LS160A and LS161A) occur as a result of,

and synchronous with, the LOW to HIGH transition of the

Clock input (CP). As long as the set-up time requirements are

met, there are no special timing or activity constraints on any

of the mode control or data inputs.

Three control inputs — Parallel Enable (PE), Count Enable

Parallel (CEP) and Count Enable Trickle (CET) — select the

mode of operation as shown in the tables below. The Count

Mode is enabled when the CEP, CET, and PE inputs are HIGH.

When the PE is LOW, the counters will synchronously load the

data from the parallel inputs into the flip-flops on the LOW to

HIGH transition of the clock. Either the CEP or CET can be

used to inhibit the count sequence. With the PE held HIGH, a

LOW on either the CEP or CET inputs at least one set-up time

prior to the LOW to HIGH clock transition will cause the

existing output states to be retained. The AND feature of the

two Count Enable inputs (CET

CEP) allows synchronous

cascading without external gating and without delay accu-

mulation over any practical number of bits or digits.

The Terminal Count (TC) output is HIGH when the Count

Enable Trickle (CET) input is HIGH while the counter is in its

maximum count state (HLLH for the BCD counters, HHHH for

the Binary counters). Note that TC is fully decoded and will,

therefore, be HIGH only for one count state.

The LS160A and LS162A count modulo 10 following a

binary coded decimal (BCD) sequence. They generate a TC

output when the CET input is HIGH while the counter is in state

9 (HLLH). From this state they increment to state 0 (LLLL). If

loaded with a code in excess of 9 they return to their legitimate

sequence within two counts, as explained in the state

diagram. States 10 through 15 do

not

generate a TC output.

The LS161A and LS163A count modulo 16 following a

binary sequence. They generate a TC when the CET input is

HIGH while the counter is in state 15 (HHHH). From this state

they increment to state 0 (LLLL).

The Master Reset (MR) of the LS160A and LS161A is

asynchronous. When the MR is LOW, it overrides all other

input conditions and sets the outputs LOW. The MR pin should

never be left open. If not used, the MR pin should be tied

through a resistor to VCC, or to a gate output which is

permanently set to a HIGH logic level.

The active LOW Synchronous Reset (SR) input of the

LS162A and LS163A acts as an edge-triggered control input,

overriding CET, CEP and PE, and resetting the four counter

flip-flops on the LOW to HIGH transition of the clock. This

simplifies the design from race-free logic controlled reset

circuits, e.g., to reset the counter synchronously after

reaching a predetermined value.

MODE SELECT TABLE

*SR

PE

CET

CEP

Action on the Rising Clock Edge ( )

L

H

H

H

H

X

L

H

H

H

X

X

H

L

X

X

X

H

X

L

RESET (Clear)

LOAD (Pn

o

Qn)

COUNT (Increment)

NO CHANGE (Hold)

NO CHANGE (Hold)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN54LS165 | 8-BIT PARALLEL-TO-SERIAL SHIFT REGISTER |

| SN54LS166 | 8-BIT SHIFT REGISTERS |

| SN54LS166J | 8-BIT SHIFT REGISTERS |

| SN74LS166D | 3.3 - 3.9GHz 1 Watt High Linearity Amplifier |

| SN74LS166N | 1.7 - 2.7GHz 2 Watt High Linearity Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74LS166AD | 功能描述:計(jì)數(shù)器移位寄存器 Serial-out shift Registers RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| SN74LS166ADE4 | 功能描述:計(jì)數(shù)器移位寄存器 Serial-out shift Registers RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| SN74LS166ADG4 | 功能描述:計(jì)數(shù)器移位寄存器 Serial Out Shift Registers RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| SN74LS166ADR | 功能描述:計(jì)數(shù)器移位寄存器 Serial-out shift Registers RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| SN74LS166ADRE4 | 功能描述:計(jì)數(shù)器移位寄存器 Serial-out shift Registers RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。