- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385870 > ST6391 (意法半導體) 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD PDF資料下載

參數(shù)資料

| 型號: | ST6391 |

| 廠商: | 意法半導體 |

| 英文描述: | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| 中文描述: | 8位微控制器HCMOS電視頻率合成帶OSD |

| 文件頁數(shù): | 20/68頁 |

| 文件大?。?/td> | 560K |

| 代理商: | ST6391 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

MEMORY SPACES

(Continued)

EEPROM Description

The dataspace of ST639xfamily from 00h to 3Fh

is paged as described in Table 5. 384 bytes of

EEPROM located in six pages of 64 bytes (pages

0,1,2,3,4 and 5, see Table 5).

Through the programming of the Data RAM Bank

Register (DRBR=E8h) the user can select the

bank or page leaving unaffected the way to ad-

dress the static registers. The way to address the

“dynamic”page is to set the DRBR as describedin

Table 5(e.g.to selectEEPROMpage 0,the DRBR

has to be loaded with content 01h, see Data

RAM/EEPROM/OSD RAM addressing for addi-

tional information).Bits0, 1 and 7of the DRBR are

dedicated tothe EEPROM.

The EEPROM pages do not require dedicated in-

structions to be accessedin readingor writing. The

EEPROM is controlled by the EEPROM Control

Register (EECR=EAh). Any EEPROM location can

be readjustlikeanyotherdatalocation,alsoin terms

of accesstime.

To write an EEPROM location takes an average

time of 5 ms (10ms max) and during this time the

EEPROM is not accessible by the Core. A busy

flag canbe readbythe Coreto knowthe EEPROM

status before trying any access. In writing the

EEPROM can work in two modes: Byte Mode

(BMODE) and Parallel Mode (PMODE). The

BMODE is the normal way to use the EEPROM

and consistsin accessing one byte at a time. The

PMODE consists inaccessing 8 bytesper time.

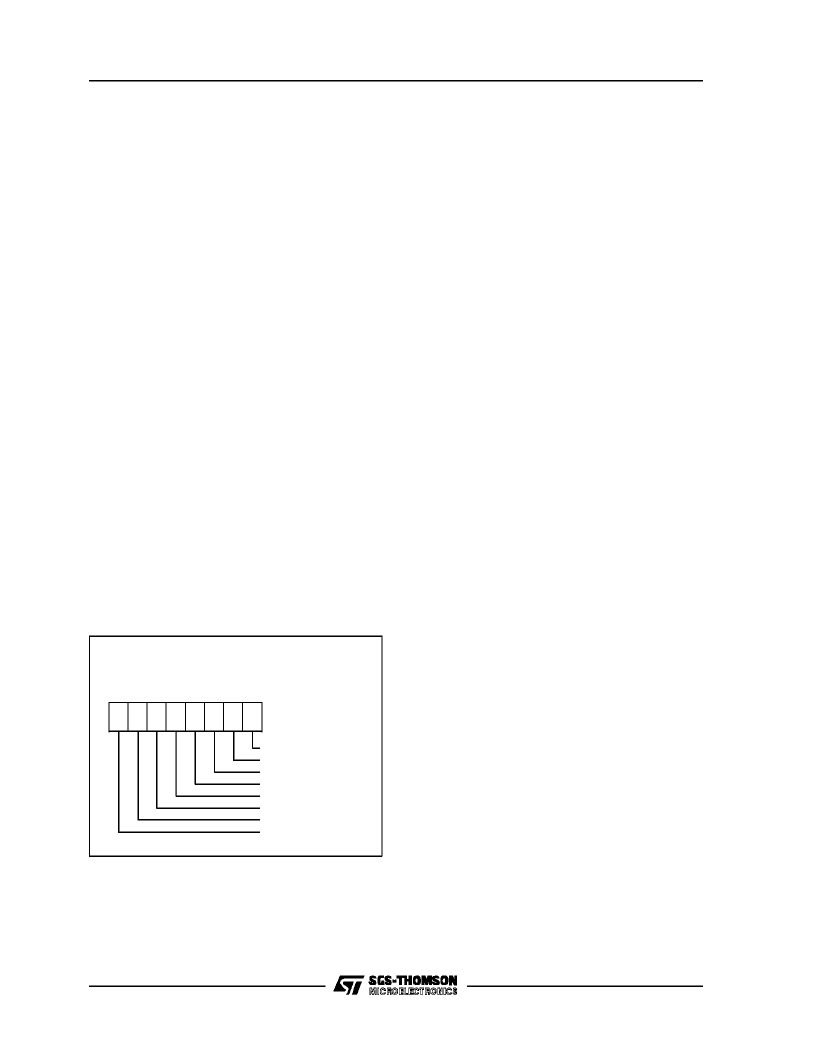

EECR

EEPROM Control Register

(EAh, Read/Write)

D7 D6 D5 D4 D3 D2 D1 D0

EN = EEPROMEnable Bit

BS =EEPROM Busy Bit

PE =Parallel Mode Enable Bit

PS =Parallel Start Bit

Reserved (Mustbe set Low)

Reserved (Mustbe set Low)

SB =Stand-by Enable Bit

Unused

Figure19. EEPROM Control Register

D7.

Not used

SB.

WRITE ONLY

.

Ifthis bit is set theEEPROM is

disabled(anyaccesswill bemeaningless)and the

power consumption of the EEPROMis reduced to

the leakage values.

D5, D4.

Reserved for testingpurposes, they must

be setto zero.

PS.

SETONLY

.

Oncein Parallel Mode,assoonas

the usersoftwaresetsthe PSbitthe parallelwriting

of the8adjacent registerswill start.PSis internally

reset at the end of the programming procedure.

Note that less than 8 bytes can be written; after

parallel programming the remaining undefined

bytes will haveno particular content.

PE.

WRITE ONLY

.

This bit must be set by the

user programin orderto performparallelprogram-

ming (more bytes per time). If PE is set and the

“parallelstartbit”(PS)is low,upto 8adjacentbytes

can be writtenat the maximumspeed, the content

being storedin volatile registers.These 8 adjacent

bytes can be considered as row, whose A7, A6,

A5, A4, A3 are fixed while A2, A1 and A0 are the

changing bytes. PE is automatically reset at the

end of any parallel programming procedure. PE

can be reset by the user software before starting

the programming procedure, leaving unchanged

the EEPROM registers.

BS.

READ ONLY

.

This bitwill be automaticallyset

by the CORE when the user program modifies an

EEPROMregister. The user program has to test it

before any read or write EEPROM operation; any

attemptto access the EEPROMwhile “busy bit” is

setwill beabortedandthewriting procedureinpro-

gress completed.

EN

. WRITE ONLY. This bit MUSTbe setto one in

order to write any EEPROM register. If the user

program will attempt to write the EEPROM when

EN= “0” the involved registers will be unaffected

and the “busy bit”will not be set.

AfterRESETthecontentofEECRregisterwillbe00h.

Notes :

When the EEPROM is busy (BS=“1”) the EECR

can notbe accessed inwrite mode, itis onlypossi-

ble to read BS status.This implies that as long as

the EEPROM is busy it is not possible to change

the status of the EEPROMcontrol register. EECR

bits 4 and 5 are reserved for test purposes, and

must never be setto “1”.

ST6391,92,93,95,97,99

16/64

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST6392B1 | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6393B1 | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6395B1 | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6391B1 | MOSFET; Transistor Polarity:Dual N Channel; Continuous Drain Current, Id:2.6A; On-Resistance, Rds(on):0.18ohm; Package/Case:8-SOIC; Leaded Process Compatible:No; Mounting Type:surface mount; Peak Reflow Compatible (260 C):No |

| ST6392 | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST6391B1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6392 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6392B1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6393 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6393B1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

發(fā)布緊急采購,3分鐘左右您將得到回復。