- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385870 > ST6391B1 (意法半導(dǎo)體) MOSFET; Transistor Polarity:Dual N Channel; Continuous Drain Current, Id:2.6A; On-Resistance, Rds(on):0.18ohm; Package/Case:8-SOIC; Leaded Process Compatible:No; Mounting Type:surface mount; Peak Reflow Compatible (260 C):No PDF資料下載

參數(shù)資料

| 型號(hào): | ST6391B1 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | MOSFET; Transistor Polarity:Dual N Channel; Continuous Drain Current, Id:2.6A; On-Resistance, Rds(on):0.18ohm; Package/Case:8-SOIC; Leaded Process Compatible:No; Mounting Type:surface mount; Peak Reflow Compatible (260 C):No |

| 中文描述: | 8位微控制器HCMOS電視頻率合成帶OSD |

| 文件頁(yè)數(shù): | 18/68頁(yè) |

| 文件大?。?/td> | 560K |

| 代理商: | ST6391B1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

MEMORY SPACES

(Continued)

Data ROM Addressing.

Allthe read-only data are

physicallyimplementedin theROM inwhich thePro-

gramSpaceis alsoimplemented.TheROMtherefore

containstheprogramtobeexecutedandalsothecon-

stantsandthelook-uptablesneededfortheprogram.

ThelocationsofDataSpaceinwhichthedifferentcon-

stants and look-up tables are addressed by the

ST639xCore can be considered as being a 64-byte

window throughwhich it is possibleto accessto the

read-onlydatastoredintheROM.This window is lo-

catedfromthe40haddressto the7Fhaddressinthe

Dataspaceandallowsthedirect readingofthebytes

from the 000h address to the 03Fh address in the

ROM.All the bytesoftheROMcanbe usedto store

eitherinstructionsorread-onlydata.Indeed,thewin-

dowcanbemovedbystepof64bytesalongtheROM

in writing the appropriatecodein theWrite-onlyData

ROMWindowregister(DRWR, locationC9h).Theef-

fectiveaddressof thebytetobe readasa datainthe

ROM is obtained by the concatenationof the 6 less

significantbits of the address in the Data Space(as

lesssignificant bits) and thecontentoftheDRWR (as

most significant bits). So when addressing location

40hofdataspace,and0 isloadedintheDRWR, the

physicaladdressedlocationinROM is00h.

Note.

The dataROM window cannot addresswin-

dows abovethe 16k byte range.

DWR

Data ROMWindow Register

(C9h, Write Only)

D7 D6 D5 D4 D3 D2 D1 D0

DWR0 = Data ROMWindow 0

DWR1 = Data ROMWindow 1

DWR2 = Data ROMWindow 2

DWR3 = Data ROMWindow 3

DWR4 = Data ROMWindow 4

DWR5 = Data ROMWindow 5

DWR6 = Data ROMWindow 6

DWR7 = Data ROMWindow 7

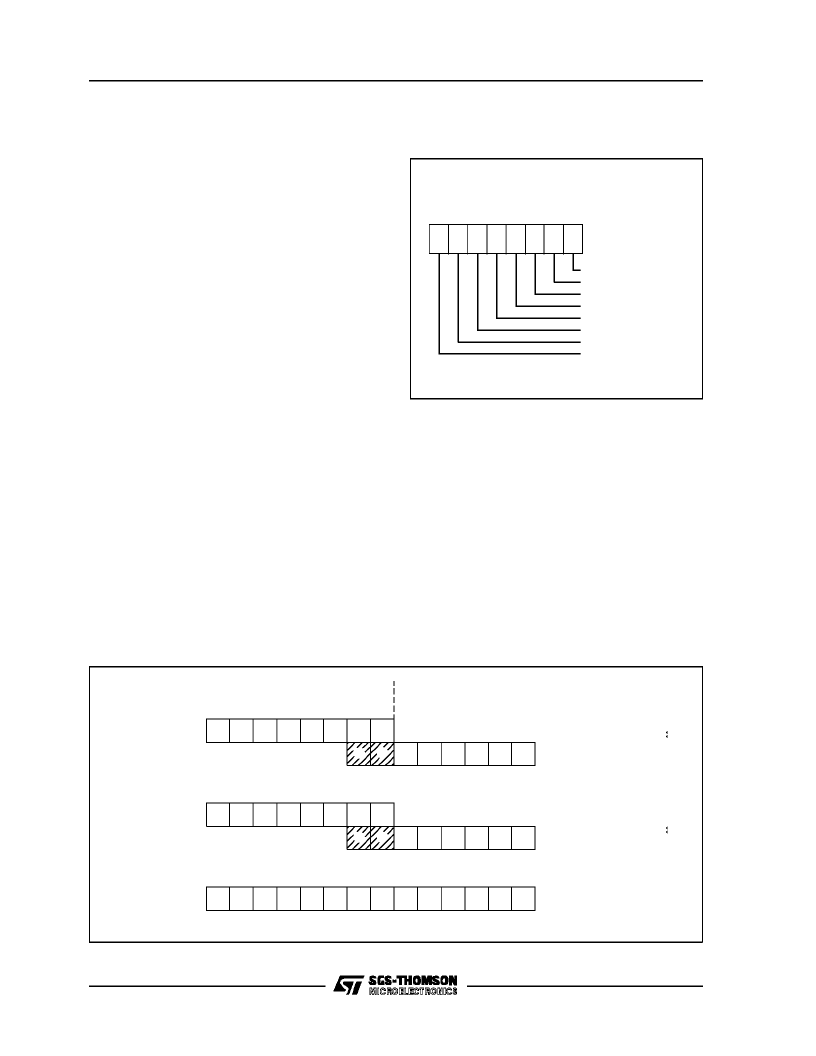

Figure 16. Data ROM Window Register

DATA ROM

WINDOW REGISTER

CONTENTS

(DWR)

DATA SPACE ADDRESS

40h-7Fh

IN INSTRUCTION

PROGRAM SPACE ADDRESS

READ

6

5

4

3

2

0

5

4

3

2

1

0

5

4

3

2

1

0

1

6

7

8

9

10

11

0

1

VR01573B

12

1

0

DATA SPACE ADDRESS

59h

0

0

0

0

0

1

0

0

1

1

1

Example:

DWR=28h

1

1

0

0

0

0

0

0

0

0

1

ROM

ADDRESS:A19h

1

1

13

0

1

7

0

0

Figure17. Data ROM Window Memory Addressing

DWR7-DWR0.

These are the Data Rom Window

bits that correspond to the upper bits of data ROM

program space.This register is undefined after re-

set.

Note.

Careis requiredwhenhandlingtheDRWR as

it is write only. For this reason, it is not allowed to

change the DRWR contents while executing inter-

ruptsdrivers, asthe drivercannot saveand than re-

store its previous content.If it is impossibleto avoid

thewriting ofthisregisterin interruptsdrivers, anim-

ageofthisregistermustbesavedinaRAMlocation,

and each time the program writes the DRWR it

writes also the image register. The image register

must be written first, so if an interrupt occurs be-

tweenthe two instructionsthe DRWR register is not

affected.

ST6391,92,93,95,97,99

14/64

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST6392 | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6393 | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6395 | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6397 | 8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6399 | MOSFET; Transistor Polarity:P Channel; Drain Source Voltage, Vds:-30V; Continuous Drain Current, Id:-4.1A; On-Resistance, Rds(on):0.08ohm; Rds(on) Test Voltage, Vgs:-10V; Package/Case:8-1206; Leaded Process Compatible:No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST6392 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6392B1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6393 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6393B1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

| ST6395 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT HCMOS MCUs FOR TV FREQUENCY SYNTHESIS WITH OSD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。