- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98145 > ST72621J2B1 (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP20 PDF資料下載

參數(shù)資料

| 型號: | ST72621J2B1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP20 |

| 封裝: | 0.300 INCH, PLASTIC, DIP-20 |

| 文件頁數(shù): | 73/136頁 |

| 文件大小: | 2475K |

| 代理商: | ST72621J2B1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當(dāng)前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁

ST7262

41/136

WATCHDOG TIMER (Cont’d)

10.1.4 Software Watchdog Option

If Software Watchdog is selected by option byte,

the watchdog is disabled following a reset. Once

activated it cannot be disabled, except by a reset.

The T6 bit can be used to generate a software re-

set (the WDGA bit is set and the T6 bit is cleared).

10.1.5 Hardware Watchdog Option

If Hardware Watchdog is selected by option byte,

the watchdog is always active and the WDGA bit in

the CR is not used.

10.1.6 Low Power Modes

WAIT Instruction

No effect on Watchdog.

HALT Instruction

Halt mode can be used when the watchdog is en-

abled. When the oscillator is stopped, the WDG

stops counting and is no longer able to generate a

reset until the microcontroller receives an external

interrupt or a reset.

If an external interrupt is received, the WDG re-

starts counting after 514 CPU clocks. In the case

of the Software Watchdog option, if a reset is gen-

erated, the WDG is disabled (reset state).

Recommendations

– Make sure that an external event is available to

wake up the microcontroller from Halt mode.

– Before executing the HALT instruction, refresh

the WDG counter, to avoid an unexpected WDG

reset immediately after waking up the microcon-

troller.

– When using an external interrupt to wake up the

microcontroller, reinitialize the corresponding I/O

as Input before executing the HALT instruction.

The main reason for this is that the I/O may be

wrongly configured due to external interference

or by an unforeseen logical condition.

– The opcode for the HALT instruction is 0x8E. To

avoid an unexpected HALT instruction due to a

program counter failure, it is advised to clear all

occurrences of the data value 0x8E from memo-

ry. For example, avoid defining a constant in

ROM with the value 0x8E.

– As the HALT instruction clears the I bit in the CC

register to allow interrupts, the user may choose

to clear all pending interrupt bits before execut-

ing the HALT instruction. This avoids entering

other peripheral interrupt routines after executing

the external interrupt routine corresponding to

the wake-up event (reset or external interrupt).

10.1.7 Interrupts

None.

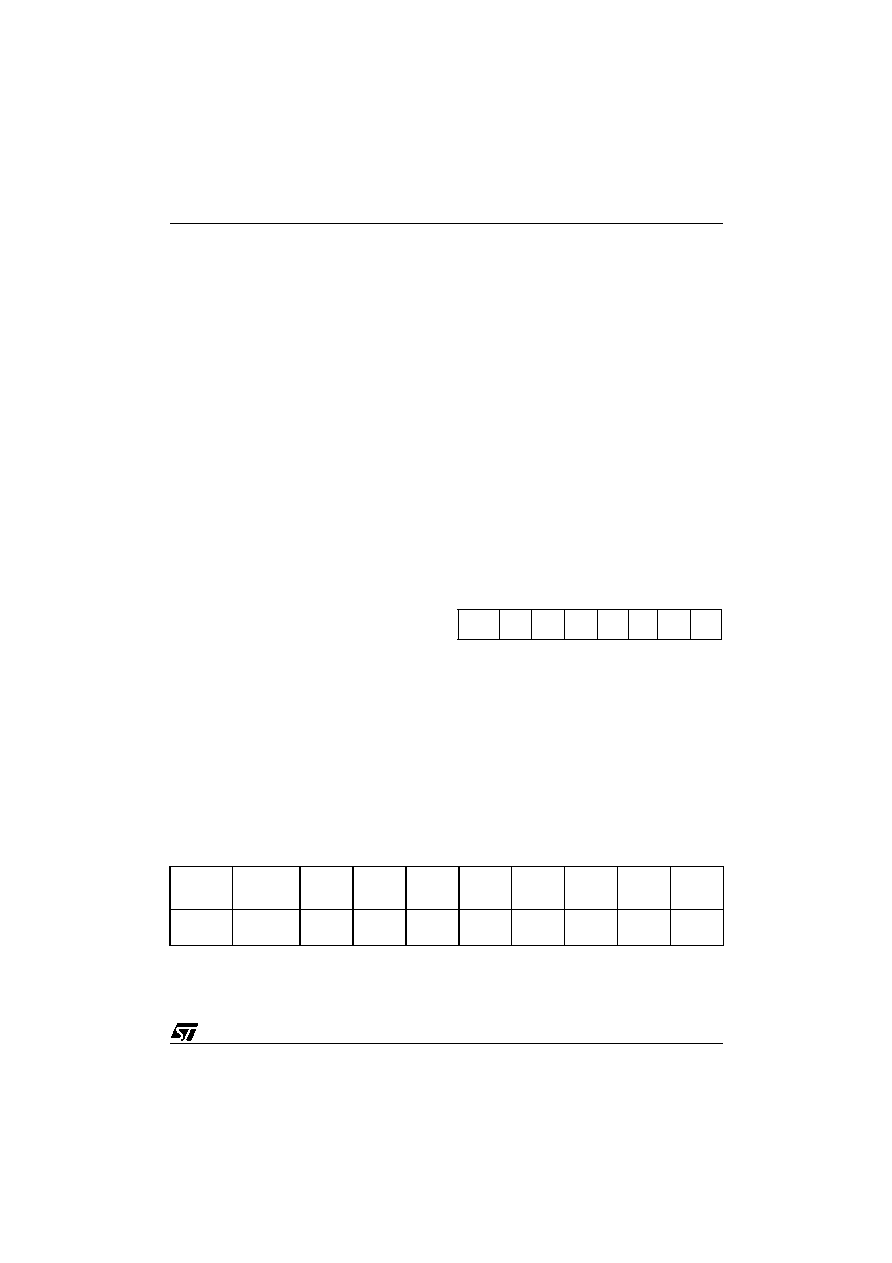

10.1.8 Register Desc4ription

CONTROL REGISTER (CR)

Read/Write

Reset Value: 0111 1111 (7Fh)

Bit 7 = WDGA Activation bit.

This bit is set by software and only cleared by

hardware after a reset. When WDGA = 1, the

watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

Note: This bit is not used if the hardware watch-

dog option is enabled by option byte.

Bits 6:0 = T[6:0] 7-bit timer (MSB to LSB).

These bits contain the decremented value. A reset

is produced when it rolls over from 40h to 3Fh (T6

becomes cleared).

Table 15. Watchdog Timer Register Map and Reset Values

70

WDGA

T6

T5

T4

T3

T2

T1

T0

Address

(Hex.)

Register

Label

765

43210

0Dh

WDGCR

Reset Value

WDGA

0

T6

1

T5

1

T4

1

T3

1

T2

1

T1

1

T0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST72621J2T1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| ST72P621L4M1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| ST72623F2M1L | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO34 |

| ST7263BK1B/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP32 |

| ST72652AR4T1/XXX | 8-BIT, MROM, MICROCONTROLLER, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST7263-EMU2 | 功能描述:仿真器/模擬器 ST7 Emulator Board RoHS:否 制造商:Blackhawk 產(chǎn)品:System Trace Emulators 工具用于評估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| ST7265X-EVAL/MS | 制造商:STMicroelectronics 功能描述:ST6 EVAL BD - Bulk |

| ST7265X-EVAL/PFD | 制造商:STMicroelectronics 功能描述:USB FLASH EVAL - Bulk |

| ST7266 | 制造商:6940 功能描述:ST7266 |

| ST7267C8T1L | 制造商:STMicroelectronics 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。