- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371182 > TDA8260 (NXP Semiconductors N.V.) Satellite Zero-IF QPSK/8PSK downconverter with PLL synthesizer PDF資料下載

參數(shù)資料

| 型號: | TDA8260 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Satellite Zero-IF QPSK/8PSK downconverter with PLL synthesizer |

| 中文描述: | 衛(wèi)星零中頻QPSK/8PSK與PLL合成器變頻器 |

| 文件頁數(shù): | 9/23頁 |

| 文件大?。?/td> | 143K |

| 代理商: | TDA8260 |

2004 Sep 03

9

Philips Semiconductors

Product specification

Satellite Zero-IF QPSK/8PSK

downconverter with PLL synthesizer

TDA8260TW

I

2

C-bus read mode

I

2

C-bus read mode: R/W = logic 1 (address LSB;

see Table 7).

Whenareadsequenceisstarted,alleightbitsofthestatus

byte must be read.

DatacanbereadfromtheTDA8260TWbysettingtheR/W

bit to logic 1. After recognition of its slave address, the

TDA8260TW generates an acknowledge pulse and

transfers the status byte onto the SDA line (MSB first).

Data is valid on the SDA line when the SCL clock signal is

HIGH.

A second data byte can be read from the TDA8260TW if

the microcontroller generates an acknowledge on the SDA

line. End of transmission will occur if no acknowledge is

received from the microcontroller. The TDA8260TW will

then release the data line to allow the microcontroller to

generate a STOP condition.

The POR flag (Power-on reset) is set to logic 1 at

power-on and when V

CC

goes below 2.7 V. It is reset to

logic 0 when an end-of-data condition is detected by the

TDA8260TW (end of a READ sequence).

The in-lock flag FL indicates that the loop is phase-locked

when set to logic 1.

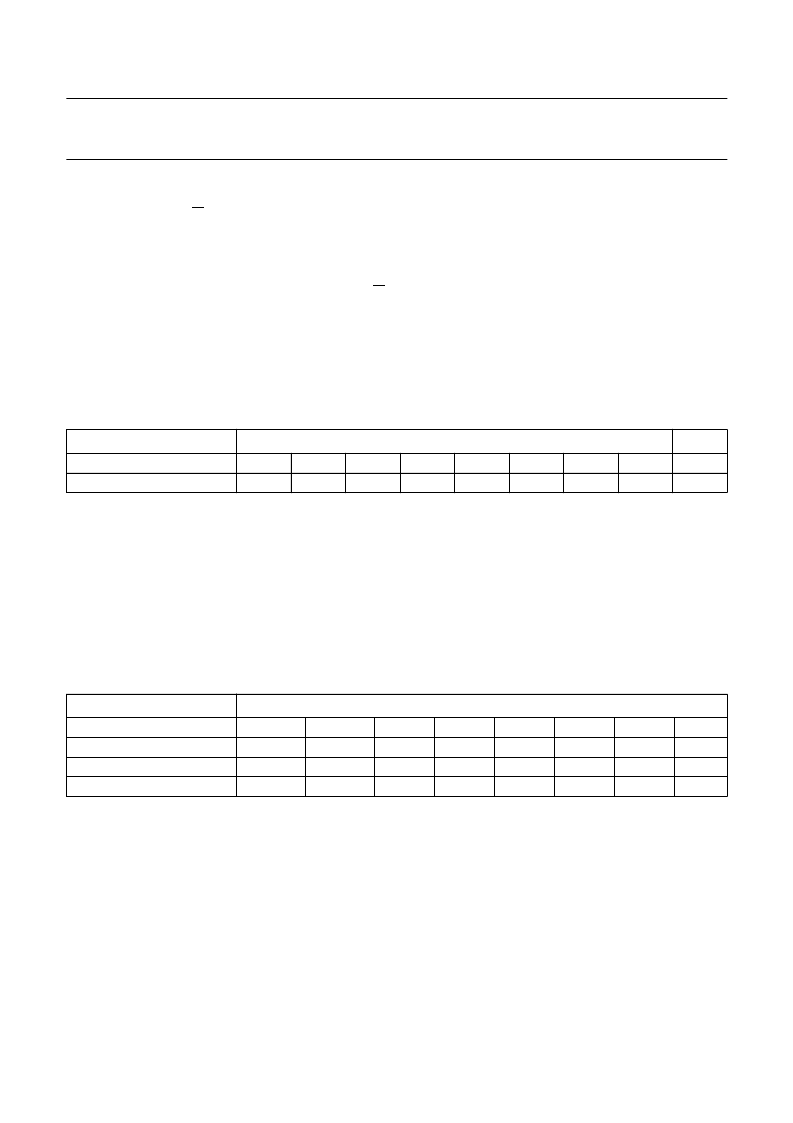

Table 7

I

2

C-bus read data format

Notes

1.

2.

3.

Acknowledge bit (A).

FL is valid only in normal mode.

X can be 1 or 0 and needs to be masked in the microcontrollers’ software; MSB is transmitted first.

P

OWER

-

ON RESET

Power-on reset flag POR = 1 at power-on.

At power-on, or when the supply voltage drops below 2.7 V, internal registers are reset as shown in Table 8.

Table 8

Status at Power-on reset

Note

1.

X = not set.

BYTE

(MSB)

BITS

(LSB)

ACK

(1)

Address

Status byte

1

1

0

0

0

MA1

X

(3)

MA0

X

(3)

1

A

POR

FL

(2)

X

(3)

X

(3)

X

(3)

X

(3)

BYTE

(MSB)

BITS

(1)

(LSB)

Programmable divider (PD1)

Programmable divider (PD2)

Control data (CD1)

Control data (CD2)

0

N14 = X

N6 = X

T2 = 0

C0 = X

N13 = X

N5 = X

T1 = 0

X

N12 = X

N4 = X

T0 = 1

X

N11 = X

N3 = X

R2 = X

X

N10 = X

N12 = X

R1 = X

X

N9 = X

N1 = X

R0 = X

X

N8 = X

N0 = X

X

X

N7 = X

1

C1 = X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TDA8260TW | Satellite Zero-IF QPSK/8PSK downconverter with PLL synthesizer |

| TDA8304 | SMALL SIGNAL COMBINATION IC FOR COLOUR TV |

| TDA8315 | Integrated NTSC decoder and sync processor |

| TDA8315T | Integrated NTSC decoder and sync processor |

| TDA8390 | PAL DECODER AND RGB MATRIX |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TDA8260TW | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Satellite Zero-IF QPSK/8PSK downconverter with PLL synthesizer |

| TDA8261TW | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Satellite Zero-IF QPSK/8PSK downconverter with PLL synthesizer |

| TDA8262HN | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Fully integrated satellite tuner |

| TDA8262HN/C1,118 | 功能描述:調(diào)諧器 INTEGRATED SATELLITE Tuner RoHS:否 制造商:NXP Semiconductors 功能: 噪聲系數(shù): 工作電源電壓: 最小工作溫度: 最大工作溫度: |

| TDA8262HN/C1-T | 功能描述:調(diào)諧器 INTEGRATED SATELLITE TUNER RoHS:否 制造商:NXP Semiconductors 功能: 噪聲系數(shù): 工作電源電壓: 最小工作溫度: 最大工作溫度: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。