- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383953 > TLC320AD535C (Texas Instruments, Inc.) DUAL CHANNEL VOICE/DATA CODEC PDF資料下載

參數(shù)資料

| 型號(hào): | TLC320AD535C |

| 廠商: | Texas Instruments, Inc. |

| 元件分類(lèi): | Codec |

| 英文描述: | DUAL CHANNEL VOICE/DATA CODEC |

| 中文描述: | 雙通道語(yǔ)音/數(shù)據(jù)編解碼器 |

| 文件頁(yè)數(shù): | 73/84頁(yè) |

| 文件大?。?/td> | 447K |

| 代理商: | TLC320AD535C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)當(dāng)前第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

B–1

Appendix B

Secondary Communications

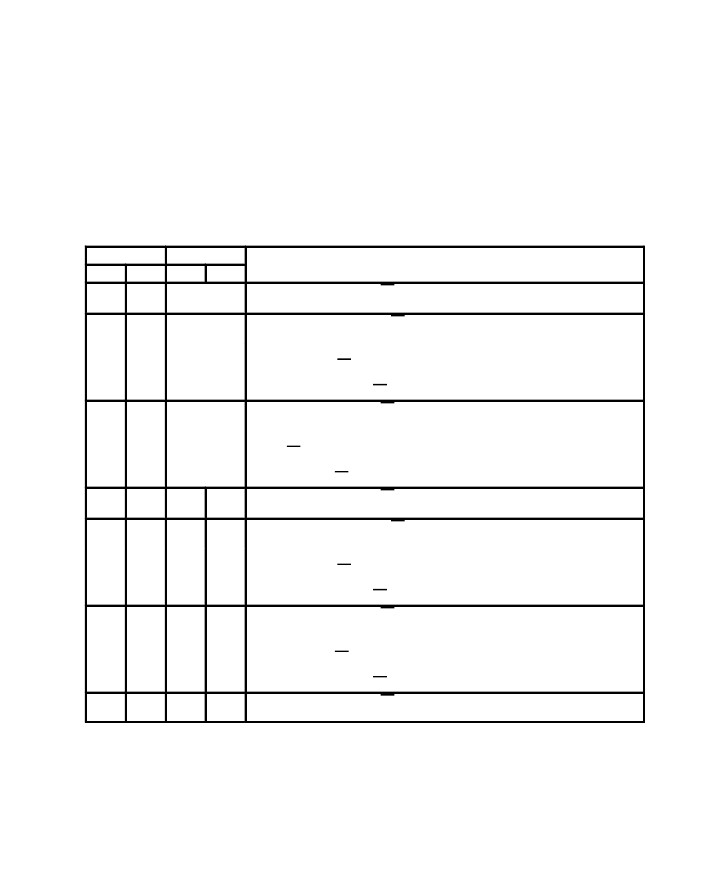

The function of the control bits DS15 and DS14 and the hardware terminals FC0 and FC1 are shown below.

Any combinational state of DS15, DS14, FC1, and FC0 not shown is ignored.

CONTROL FUNCTION OF SECONDARY COMMUNICATION

BITS

TERMINALS

FC1

DS15

DS14

FC0

0

0

Ignored

On the next falling edge of FS, the AIC receives DAC data D15–D02 at DIN and

transmits the ADC data D15–D00 from DOUT.

0

1

Ignored

On the next falling edge of the FS, the AIC receives DAC data D15–D02 at DIN and

transmits the ADC data D15–D00 from DOUT.

The phase adjustment is determined by the state of DS15 and DS14 such that on the

next rising edge of FS, the next ADC/DAC sampling time occurs later by the number

of MCLK periods determined by the value contained in the A

′

register. When the A

′

register value is negative, FS occurs earlier.

1

0

Ignored

On the next falling edge of FS, the AIC receives DAC data D15–D02 at DIN and

transmits the ADC data D15–D00 from DOUT.

The phase adjustment is determined by the state of D01 and D00. On the next rising

edge of FS, the next ADC/DAC sampling time occurs earlier by the number of MCLK

periods determined by the value contained in the A

′

register. When the A

′

register

value is negative, FS occurs later.

1

1

0

0

On the next falling edge of FS, the AIC receives DAC data D15–D02 at DIN and

transmits the ADC data D15–D00 from DOUT.

1

1

0

1

On the next falling edge of the FS, the AIC receives DAC data D15–D02 at DIN and

transmits the ADC data D15–D00 from DOUT.

The phase adjustment is determined by the state of FC1 and FC0 such that on the

next rising edge of FS, the next ADC/DAC sampling time occurs later by the number

of MCLK periods determined by the value contained in the A

′

register. When the A

′

register value is negative, FS occurs earlier.

1

1

1

0

On the next falling edge of FS, the AIC receives DAC data D15–D02 at DIN and

transmits the ADC data D15–D00 from DOUT.

The phase adjustment is determined by the state of FC1 and FC0 such that on the

next rising edge of FS, the next ADC/DAC sampling time occurs earlier by the number

of MCLK periods determined by the value contained in the A

′

register. When the A

′

register value is negative, FS occurs later.

1

1

1

1

On the next falling edge of FS, the AIC receives DAC data D15–D02 at DIN and

transmits the ADC data D15–D00 from DOUT.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC320AD535C-I | DUAL CHANNEL VOICE/DATA CODEC |

| TLC320AD535I | DUAL CHANNEL VOICE/DATA CODEC |

| TLC320AC02I | Single-Supply Analog Interface Circuit |

| TLC320AD50IPT | SIGMA-DELTA ANALOG INTERFACE CIRCUITS WITH MASTER-SLAVE FUNCTION |

| TLC320AD50(中文) | Sigma-Delta Analog Interface Circuit With Master-Slave Function(Sigma-Delta 模擬接口具主從功能) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC320AD535C-I | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:DUAL CHANNEL VOICE/DATA CODEC |

| TLC320AD535I | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:DUAL CHANNEL VOICE/DATA CODEC |

| TLC320AD535IPM | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLC320AD535PM | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLC320AD545-EVM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。