- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98243 > TLC5618CP (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, 12.5 us SETTLING TIME, 12-BIT DAC, PDIP8 PDF資料下載

參數(shù)資料

| 型號(hào): | TLC5618CP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類(lèi): | DAC |

| 英文描述: | SERIAL INPUT LOADING, 12.5 us SETTLING TIME, 12-BIT DAC, PDIP8 |

| 封裝: | PLASTIC, DIP-8 |

| 文件頁(yè)數(shù): | 7/26頁(yè) |

| 文件大小: | 386K |

| 代理商: | TLC5618CP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

TLC5618, TLC5618A

PROGRAMMABLE DUAL 12-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS156G – JULY 1997 – REVISED APRIL 2001

15

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

APPLICATION INFORMATION

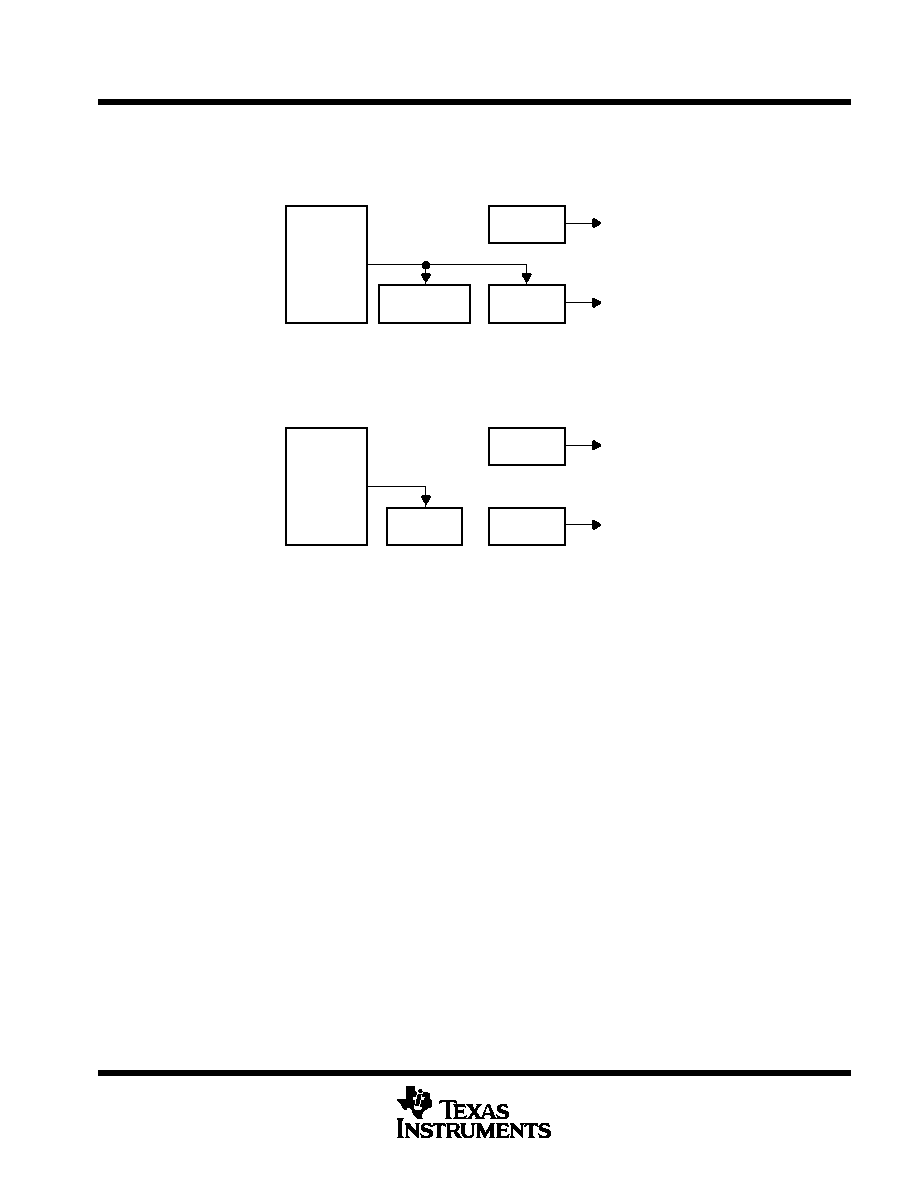

latch B and double-buffer 1 write (D15 = low, D12 = low)

The SIR data are written to both latch B and the double buffer. Latch A is unaffected.

Serial

Interface

Register

D12 = Low

D15 = Low

Latch A

Latch B

Double

Buffer Latch

To DAC A

To DAC B

Figure 20. Latch B and Double-Buffer Write

double-buffer-only write (D15 = low, D12 = high)

The SIR data are written to the double buffer only. Latch A and B contents are unaffected.

Serial

Interface

Register

D12 = High

D15 = Low

Latch A

Latch B

Double

Buffer

To DAC A

To DAC B

purpose and use of the double buffer

Normally only one DAC output can change after a write. The double buffer allows both DAC outputs to change

after a single write. This is achieved by the two following steps.

1.

A double-buffer-only write is executed to store the new DAC B data without changing the DAC A and B

outputs.

2.

Following the previous step, a write to latch A is executed. This writes the SIR data to latch A and also

writes the double-buffer contents to latch B. Thus both DACs receive their new data at the same time,

and so both DAC outputs begin to change at the same time.

Unless a double-buffer-only write is issued, the latch B and double-buffer contents are identical. Thus, following

a write to latch A or B with another write to latch A does not change the latch B contents.

operational examples

changing the latch A data from zero to full code

Assuming that latch A starts at zero code (e.g., after power up), the latch can be filled with 1s by writing (bit D15

on the left, D0 on the right)

1X0X 1111 1111 1111

to the serial interface. Bit D14 can be zero to select slow mode or one to select fast mode. The other X can be

zero or one (don’t care).

The latch B contents and the DAC B output are not changed by this write unless the double-buffer contents are

different from the latch B contents. This can only be true if the last write was a double-buffer-only write.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC5618AMFK | SERIAL INPUT LOADING, 12.5 us SETTLING TIME, 12-BIT DAC, CQCC20 |

| TLC5618IP | SERIAL INPUT LOADING, 12.5 us SETTLING TIME, 12-BIT DAC, PDIP8 |

| TLC5620CN | SERIAL INPUT LOADING, 10 us SETTLING TIME, 8-BIT DAC, PDIP14 |

| TLC5620CDR | SERIAL INPUT LOADING, 10 us SETTLING TIME, 8-BIT DAC, PDSO14 |

| TLC5620IDR | SERIAL INPUT LOADING, 10 us SETTLING TIME, 8-BIT DAC, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC5618ID | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TLC5618IDR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PROGRAMMABLE DUAL 12-BIT DIGITAL-TO-ANALOG CONVERTERS |

| TLC5618IP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PROGRAMMABLE DUAL 12-BIT DIGITAL-TO-ANALOG CONVERTERS |

| TLC5620 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:QUADRUPLE 8-BIT DIGITAL-TO-ANALOG CONVERTERS |

| TLC5620C | 制造商:TI 制造商全稱:Texas Instruments 功能描述:QUADRUPLE 8-BIT DIGITAL-TO-ANALOG CONVERTERS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。