- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98252 > TLV2556IPW (TEXAS INSTRUMENTS INC) 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | TLV2556IPW |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | GREEN, PLASTIC, TSSOP-20 |

| 文件頁數(shù): | 20/37頁 |

| 文件大?。?/td> | 729K |

| 代理商: | TLV2556IPW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

TLV2556

SLAS355A – DECEMBER 2001 – REVISED SEPTEMBER 2002

27

www.ti.com

PRINCIPLES OF OPERATION

conversion cycle

A conversion cycle is started only after the I/O cycle is completed, which minimizes the influence of external

digital noise on the accuracy of the conversion. This cycle is transparent to the user because it is controlled by

an internal clock (oscillator). The total conversion time is equal to 13.5 OSC clocks plus a small delay (~25 ns)

to start the OSC. During the conversion period, the device performs a successive-approximation conversion

on the analog input voltage.

When programmed as EOC, pin 19 goes low at the start of the conversion cycle and goes high when the

conversion is complete and the output data register is latched. After EOC goes low, the analog input can be

changed without affecting the conversion result. Since the delay from the falling edge of the last I/O CLOCK to

the falling edge of EOC is fixed, any time-varying analog input signals can be digitized at a fixed rate without

introducing systematic harmonic distortion or noise due to timing uncertainty.

When programmed as INT, pin 19 goes low when the conversion is complete and the output data register is

latched. The next I/O CLOCK rising edge clears the INT output. The time from the last I/O CLOCK falling edge

to the falling INT edge is equivalent to the EOC delay mentioned above plus the maximum conversion time. INT

is cancelled by (or brought to high) by either the next CS falling edge or the next SCLK rising edge (when CS

is held low all of the time for multiple cycles). When CS is held low continuously (for multiple cycles) MSB output

occurs after the first rising edge of I/O CLOCK after EOC is inactive or the falling edge of INT.

power up and initialization

After power up, CS must be taken from high to low to begin an I/O cycle. INT/EOC pin is initially high, and both

configuration registers are set to all zeroes. The contents of the output data register are random, and the first

conversion result should be ignored. To initialize during operation, CS is taken high and is then returned low

to begin the next I/O cycle. The first conversion after the device has returned from the power-down state may

not read accurately due to internal device settling.

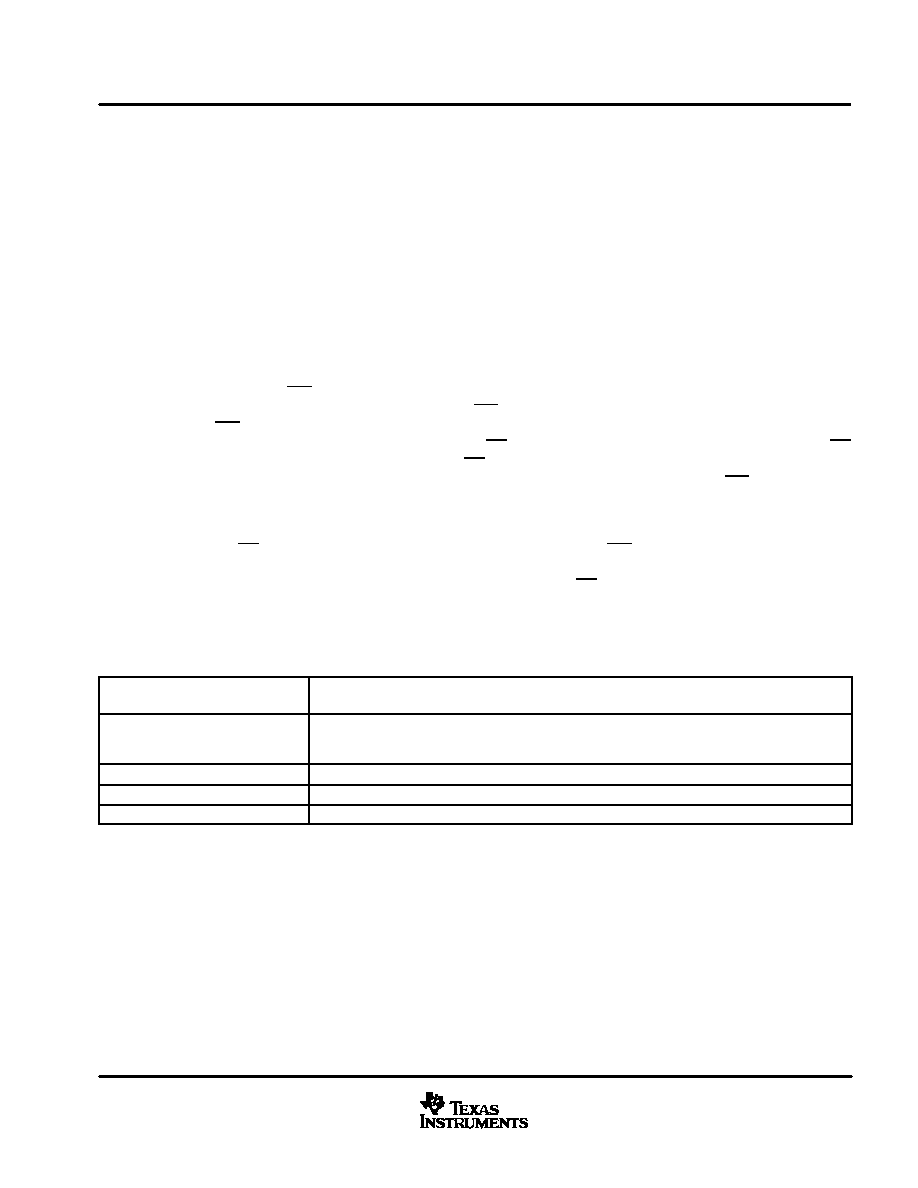

Table 1. Operational Terminology

Current (N) I/O cycle

The entire I/O CLOCK sequence that transfers address and control data into the data register and clocks

the digital result from the previous conversion from DATA OUT.

Current (N) conversion cycle

The conversion cycle starts immediately after the current I/O cycle. The end of the current I/O cycle is the

last clock falling edge in the I/O CLOCK sequence. The current conversion result is loaded into the out-

put register when conversion is complete.

Current (N) conversion result

The current conversion result is serially shifted out on the next I/O cycle.

Previous (N–1) conversion cycle

The conversion cycle just prior to the current I/O cycle

Next (N+1) I/O cycle

The I/O period that follows the current conversion cycle

Example:

In 12-bit mode, the result of the current conversion cycle is a 12-bit serial-data stream clocked out during the

next I/O cycle. The current I/O cycle must be exactly 12 bits long to maintain synchronization, even when this

corrupts the output data from the previous conversion. The current conversion is begun immediately after the

twelfth falling edge of the current I/O cycle.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV2556IDWR | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556IPWR | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556IDW | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556IPWG4 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556MPWREP | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV2556IPW | 制造商:Texas Instruments 功能描述:12BIT ADC 200KSPS 2556 TSSOP20 制造商:Texas Instruments 功能描述:12BIT ADC, 200KSPS, 2556, TSSOP20 制造商:Texas Instruments 功能描述:12BIT ADC, 200KSPS, 2556, TSSOP20; Resolution (Bits):12bit; Sampling Rate:200kSPS; Supply Voltage Type:Single; Supply Voltage Min:2.7V; Supply Voltage Max:5.5V; Supply Current:3mA; Digital IC Case Style:TSSOP; No. of Pins:20; Input ;RoHS Compliant: Yes |

| TLV2556IPWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2556IPWR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2556IPWRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2556MPWREP | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC EP 12B,200KSPS,11Ch Low Pwr,Serial ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。