- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98252 > TLV320AIC14I (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PDSO30 PDF資料下載

參數(shù)資料

| 型號(hào): | TLV320AIC14I |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO30 |

| 封裝: | PLASTIC, TSSOP-30 |

| 文件頁(yè)數(shù): | 17/54頁(yè) |

| 文件大?。?/td> | 450K |

| 代理商: | TLV320AIC14I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

3–11

3.8

Smart Time Division Multiplexed Serial Port (SMARTDM)

The SMART time division multiplexed serial port (SMARTDM) uses the 4 wires of DOUT, DIN, SCLK, and FS to

transfer data into and out of the AIC14. The TLV320AIC14s SMARTDM supports three serial interface configurations

(see Table 3–2): stand-alone master, stand-alone slave, and master-slave cascade, employing a time division

multiplexed (TDM) scheme (a cascade of only-slaves is not supported). The SMARTDM allows for a serial connection

of up to 16 codecs to a single serial port. Data communication in these three serial interface configurations can be

carried out in either standard operation (default) or turbo operation. Each operation has two modes; programming

mode (default mode) and continuous data transfer mode. To switch from the programming mode to the continuous

data transfer mode, set bit D6 of control register 1 to 1, which resets after switching back to programming mode. The

TLV320AIC14 can be switched back from the continuous data transfer mode to the programming mode by setting

the LSB of the data on DIN to 1, only if the data format is (15+1), as selected by bit 0 of control register 1. The

SMARTDM automatically adjusts the number of time slots per frame sync (FS) to match the number of codecs in the

serial interface so that no time slot is wasted. Both the programming mode and the continuous data transfer mode

of the TLV320AIC14 are compatible with the TLV320AIC10. The TLV320AIC14 provides primary/secondary

communication and continuous data transfer with improvements and eliminates the requirements for hardware and

software requests for secondary communication as seen in the TLV320AIC10. The TLV320AIC14 continuous data

transfer mode now supports both master/slave stand-alone and cascade.

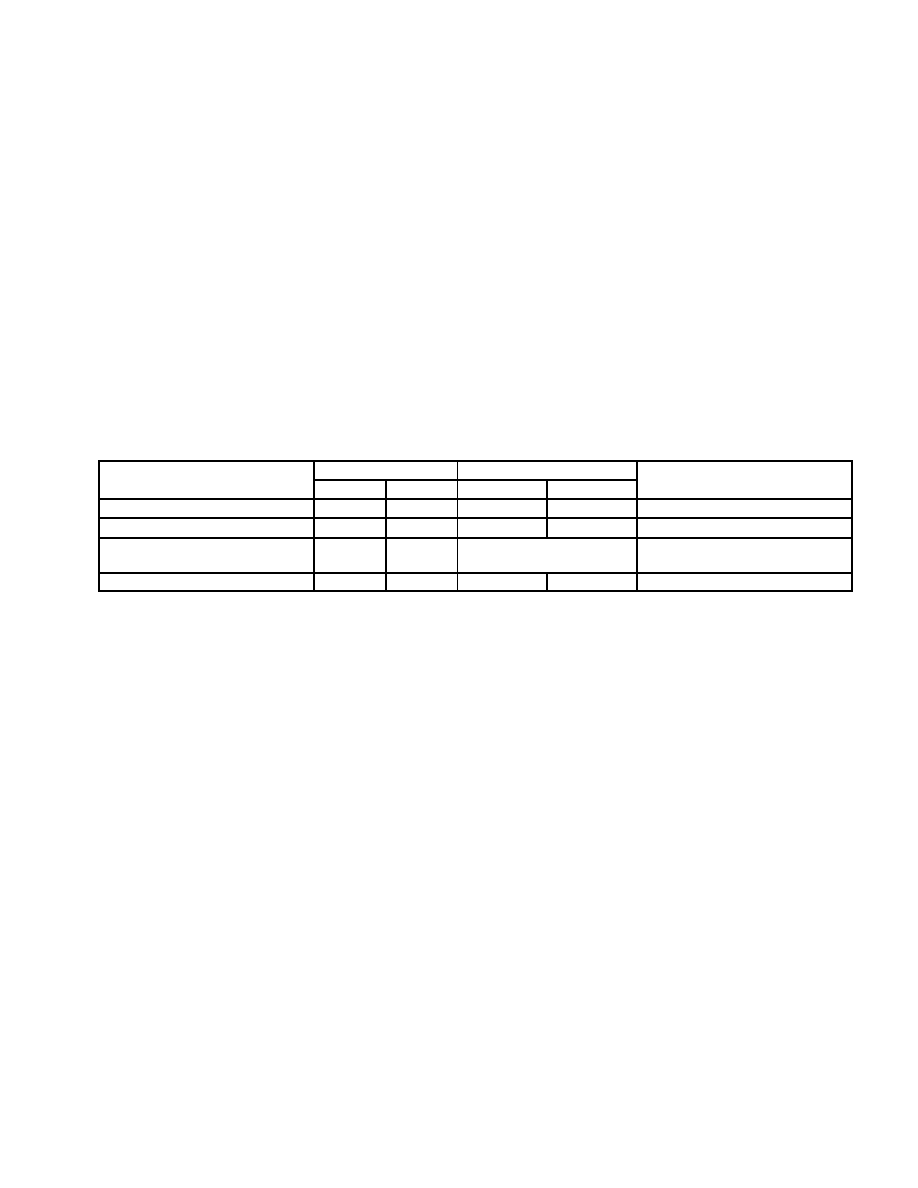

Table 3–2. Serial Interface Configurations

TLV320AIC14

M/S PIN

FSD PIN

COMMENTS

TLV320AIC14

CONNECTIONS

MASTER

SLAVE

MASTER

SLAVE

COMMENTS

Stand-alone master

High

NA

Pull high

NA

Stand-alone slave

NA

Low

NA

Pull-low

Master-slave cascade

High

Low

Connect to the next slave’s FS

(see Figure 3–7)

Last slave’s FSD pin is pulled high

Slave-slave cascade

NA

Not supported

3.8.1

Programming Mode

In the programming mode, the FS signal starts the input/output data stream. Each period of FS contains two frames

as shown in Figures 3–13 and 3–14: data frame and control frame. The data frame contains data transmitted from

the ADC or to the DAC. The control frame contains data to program the AIC14s control registers. The SMARTDM

automatically sets the number of time slots per frame equal to 2 times the number of AIC14 codecs in the interface.

Each time slot contains 16-bit data. The SCLK is used to perform data transfer for the serial interface between the

AIC14 codecs and the DSP. The frequency of SCLK varies depending on the selected mode of serial interface. In

the stand-alone mode, there are 32 SCLKs (or two time slots) per sampling period. In the master-slave cascade

mode, the number of SLCKs equals 32x(Number of codecs in the cascade). The digital output data from the ADC

is taken from DOUT. The digital input data for the DAC is applied to DIN. The synchronization clock for the serial

communication data and the frame-sync is taken from SCLK. The frame-sync signal that starts the ADC and DAC

data transfer interval is taken from FS. The SMARTDM also provides a turbo mode, in which the FS’s frequency is

always the device’s sampling frequency, but SCLK is running at a much higher speed. Thus, there are more than 32

SCLKs per sampling period, in which the data frame and control frame occupy only the first 32 SCLKs from the falling

edge of the frame-sync FS (also see Section 3.6 for more details).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC22PT | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC22PTR | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC23BGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC23BIGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC23BIPW | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC14IDBT | 功能描述:接口—CODEC Lo-Pwr Mono Voice Band CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC14IDBT-1 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TLV320AIC14IDBTG4 | 功能描述:接口—CODEC Lo-Pwr Mono Voice Band CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC14IDBTR | 功能描述:接口—CODEC Lo-Pwr Mono Voice Band CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC14IDBTRG4 | 功能描述:接口—CODEC Lo-Pwr Mono Voice Band CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。