- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98252 > TLV320AIC22PT (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | TLV320AIC22PT |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | ROHS COMPLIANT, PLASTIC, LQFP-48 |

| 文件頁數(shù): | 48/55頁 |

| 文件大小: | 782K |

| 代理商: | TLV320AIC22PT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

TLV320AIC22

DUAL VOIP CODEC

SLAS281B – JULY 2000 – REVISED JUNE 2002

52

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

APPLICATION INFORMATION

TLV320AIC22 DAC path-clipping avoidance

If large signals are input to either codec’s DAC at the DIN pin, internal clipping of the signals can occur. The result

is undesired signal distortion at the analog output of each DAC. To avoid signal distortion induced by clipping

in the TLV320AIC22 DAC path, the following is recommended:

1.

For linear operation:

D Always reduce the DAC signal input levels by 6 dB for each codec. This will ensure that large signals

approaching digital full-scale amplitude will not cause clipping.

D Program each codec’s internal programmable gain amplifier (PGA) for the desired overall channel gain,

plus 6 dB. The PGA for codec 1 is programmed via control register 3. The PGA for codec 2 is programmed

via control register 8.

Examples are provided in Table 16.

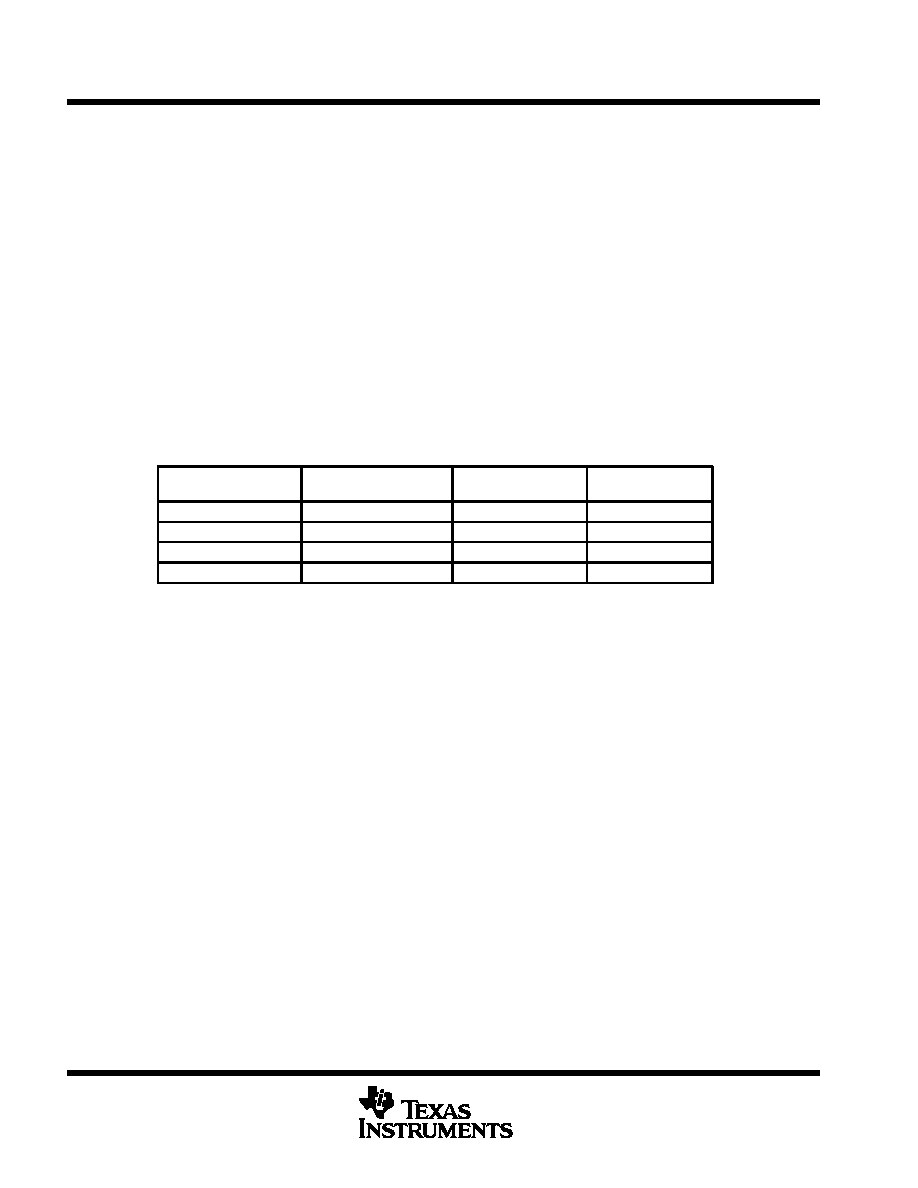

Table 16. Examples of Signal Attenuation and PGA Gain Settings

for Various Overall Channel Gains

OVERALL DESIRED

CHANNEL GAIN

INPUT LEVEL BEFORE

–6-dB APPLICATION

INPUT LEVEL AFTER

–6-dB APPLICATION

PGA GAIN

0 dB

–6 dB

6 dB

0 dB

–6 dB

–12 dB

6 dB

–27 dB

0 dB

–6 dB

–21 dB

–27 dB

–12 dB

–18 dB

–21 dB

2.

PCM companded (

-Law or A-Law) operation:

Because

-Law and A-Law transmission levels often are referenced in terms of dBm0, receive channel-input

levels limits can be noted in terms of dBm0. The signal-level 0 dBm0 is the digital milliwatt transmission level,

as addressed in the International Telecommunication Union (ITU) specification G.711. The ITU G.711

specification also shows the theoretical load capacity of the A-Law as 3.14 dBm0 and 3.17 dBm0 for the

-Law.

D Fundamentally, apply the same procedure as outlined in step 1 for linear operation.

D When using terms of dBm0, restrict A-Law signal levels to –2.88 dBm0 and -Law signal levels to

–3.02 dBm0 signal levels. These levels correspond to A-Law and

-Law to linear mapping codes that reflect

a 6-dB or greater reduction in signal level.

performance issues associated with the recommended action to avoid signal clipping in the

TLV320AIC22

The recommended action requires the attenuation of input signals by 6 dB prior to input to either codec’s DAC

on the device. The internal DAC path PGA should be programmed so that the desired channel gain and recovery

of the 6-dB input signal attenuation is accomplished. Loss of a least significant bit (LSB) of information is typical

by attenuating digital signals by 6 dB and can result in degraded signal-to-noise (SNR) performance. For the

TLV320AIC22 DAC path, the recommended action described above to avoid signal clipping results in

degradation of SNR performance typically less than 0.5 dB for signals larger than 5 LSBs and less than 2 dB

for signals larger than 2 LSBs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC22PTR | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC23BGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC23BIGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC23BIPW | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| TLV320AIC23BPW | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC22PTR | 功能描述:接口—CODEC DUAL VOIP CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC23 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:STereo Audio CODEC, 8- to 96kHz, With Integrated Headphone Amplifier |

| TLV320AIC23_06 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC23B | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC23B_06 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

發(fā)布緊急采購,3分鐘左右您將得到回復。