- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384021 > TMS320AV220 (Texas Instruments, Inc.) Video CD MPEG Decoder(視頻CD MPEG編碼器) PDF資料下載

參數(shù)資料

| 型號: | TMS320AV220 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Video CD MPEG Decoder(視頻CD MPEG編碼器) |

| 中文描述: | 視頻CD MPEG解碼器(視頻光盤的MPEG編碼器) |

| 文件頁數(shù): | 22/31頁 |

| 文件大?。?/td> | 612K |

| 代理商: | TMS320AV220 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

TMS320AV220

VIDEO CD MPEG DECODER

SCSS016A – JUNE 1994 – REVISED JANUARY 1996

22

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

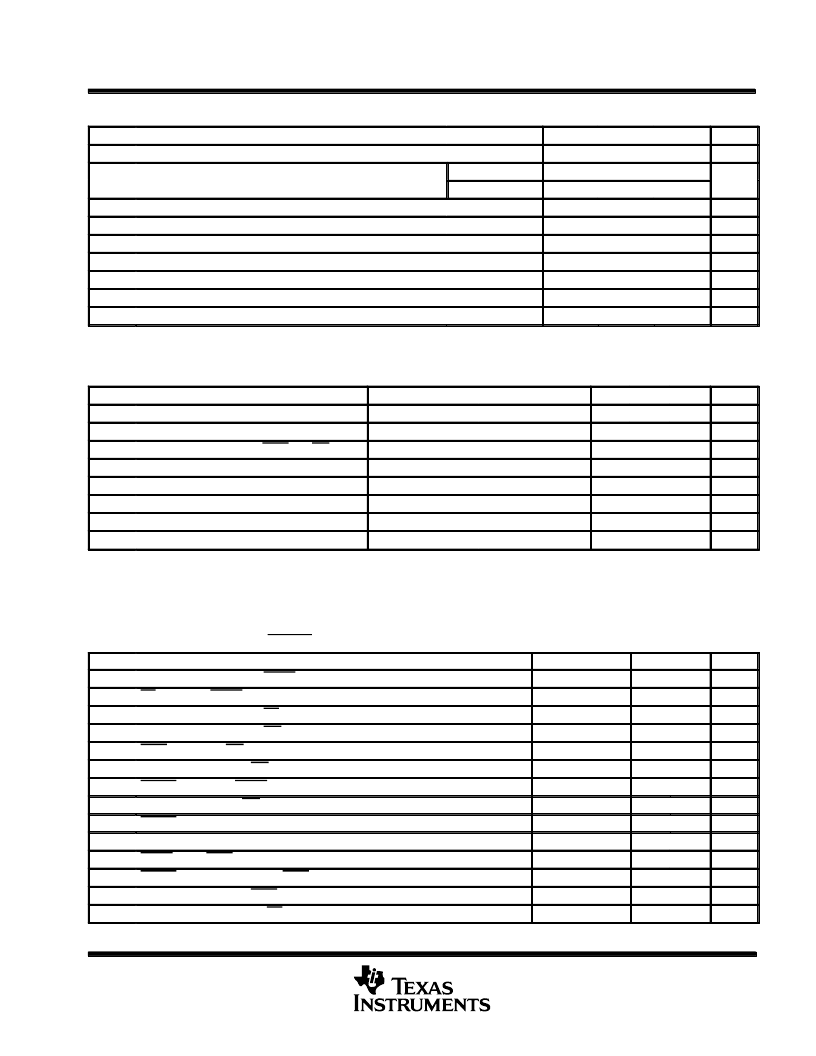

recommended operating conditions

MIN

NOM

MAX

UNIT

VCC

Supply voltage

4.75

5

5.25

V

VIH

High-level input voltage

VCLK

3.4

VCC+0.5

VCC+0.5

0.8

V

All others

2.4

VIL

IOH

IOL

fclock

fclock

dt/dV

Low-level input voltage

–0.5

V

High-level output current

–2

mA

Low-level output current

8

mA

Clock frequency, SYSCLK

40

40

MHz

Clock frequency, VCLK

13.5

14.9

MHz

Input transition (rise or fall)

5

ns/V

°

C

TA

Operating free-air temperature

0

70

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VOH

VOL

IOH

II

IOZ

ICC

Ci

Co

All typical values are at VCC = 5 V, TA = 25

°

C.

This is the capacitance at an output or I/O terminal.

High-level output voltage

VCC = 4.75 V,

VCC = 4.75 V,

VCC = 4.75 V,

VCC = 5.25 V,

VCC = 5.25 V,

VCC = 5.25 V,

f = 1 MHz

IOH = –2 mA

IOL = 8 mA

VOH = 5.25 V

VI = VCC or 0

VO = VCC or 0

SYSCLK = 40 MHz

2.8

V

Low-level output voltage

0.5

V

μ

A

μ

A

μ

A

mA

High-level output current, WAIT and INT

10

Input current

±

10

±

10

500

Off-state output current, DATAx, MDx, PDx

Supply current

380

Input capacitance

Output capacitance

10

pF

f = 1 MHz

12

pF

timing requirements and switching characteristics over recommended ranges of supply voltage

and operating free-air temperature range (unless otherwise noted)

host interface, SYSCLK and RESET timing

FIGURE

MIN

MAX

UNIT

tsu1

tsu2

tsu3

tsu4

tsu5

tsu6

tsu7

th1

tw1

tw2

tpd1

tpd2

td

tv

ADDR13–ADDR0 before MREQ low

9, 10

15

ns

CS low before MREQ low

9, 10

0

ns

ADDR13–ADDR0 before RD low

9

15

ns

ADDR13–ADDR0 before WR low

10

65

ns

WAIT high before WR high

10

50

ns

DATA7–DATA0 before WR high

10

50

ns

RESET high before MREQ low

13

2

ns

DATA7–DATA0 after WR high

10

0

ns

RESET low

13

300

ns

SYSCLK high or low

14

10

ns

MREQ low to WAIT low

9, 10

10

ns

RESET high to CDREAD and WAIT

13

25

ms

DATA7–DATA0 before WAIT high (read cycle)

9

15

ns

DATA7–DATA0 valid after RD high

9

10

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320AV410 | Digital NTSC/PAL Encoder(數(shù)字NTSC/PAL編碼器) |

| TMS320AV411 | Digital NTSC/PAL Encoder(數(shù)字NTSC/PAL編碼器) |

| TMS320AV420 | Digital NTSC Encoder(數(shù)字NTSC編碼器) |

| TMS320C6424_1 | Fixed-Point Digital Signal Processor |

| TMS320C6455ZTZ | Fixed-Point Digital Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320AV220PCM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Audio/Video Decoder for MPEG |

| TMS320AV410 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

| TMS320AV410PJM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TMS320AV411 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

| TMS320AV411PJM | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。