- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368672 > TMS320F206PZA 16-Bit Digital Signal Processor PDF資料下載

參數(shù)資料

| 型號(hào): | TMS320F206PZA |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | 16-Bit Digital Signal Processor |

| 中文描述: | 16位數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 8/57頁(yè) |

| 文件大小: | 793K |

| 代理商: | TMS320F206PZA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

TMS320F206

DIGITAL SIGNAL PROCESSOR

SPRS050A – NOVEMBER 1996 – REVISED APRIL 1998

8

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

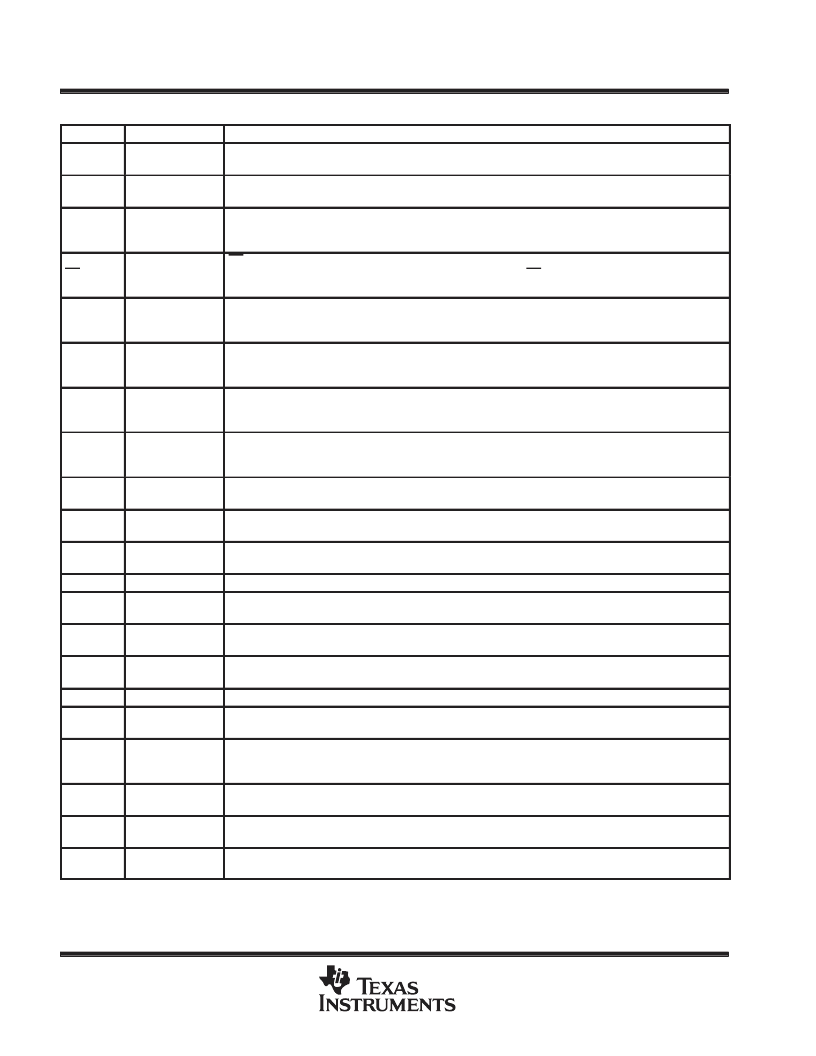

Table 2. Legend for the ’F206 Internal Hardware Functional Block Diagram

SYMBOL

NAME

DESCRIPTION

ACC

Accumulator

32-bit register that stores the results and provides input for subsequent CALU operations. Also includes shift

and rotate capabilities

ARAU

Auxiliary Register

Arithmetic Unit

An unsigned, 16-bit arithmetic unit used to calculate indirect addresses using the auxiliary registers as inputs

and outputs

AUX

REGS

Auxiliary Registers

0–7

These 16-bit registers are used as pointers to anywhere within the data space address range. They are

operated upon by the ARAU and are selected by the auxiliary register pointer (ARP). AR0 can also be used

as an index value for AR updates of more than one and as a compare value to AR.

BR

Bus Request

Signal

BR is asserted during access of the external global data memory space. READY is asserted to the device

when the global data memory is available for the bus transaction. BR can be used to extend the data memory

address space by up to 32K words.

C

Carry

Register carry output from CALU. C is fed back into the CALU for extended arithmetic operation. The C bit

resides in status register 1 (ST1), and can be tested in conditional instructions. C is also used in accumulator

shifts and rotates.

CALU

Central Arithmetic

Logic Unit

32-bit-wide main arithmetic logic unit for the TMS320C2xx core. The CALU executes 32-bit operations in a

single machine cycle. CALU operates on data coming from ISCALE or PSCALE with data from ACC, and

provides status results to PCTRL.

CNF

On-Chip RAM

Configuration

Control Bit

If set to 0, the reconfigurable data dual-access RAM (DARAM) block B0 is mapped to data space; otherwise,

B0 is mapped to program space.

GREG

Global Memory

Allocation

Register

GREG specifies the size of the global data memory space.

IMR

Interrupt Mask

Register

IMR individually masks or enables the seven interrupts.

IFR

Interrupt Flag

Register

The 7-bit IFR indicates that the TMS320F206 has latched an interrupt from one of the seven maskable

interrupts.

INTM

Interrupt-Mode Bit

When INTM is set to 0, all unmasked interrupts are enabled. When INTM is set to 1, all maskable interrupts

are disabled.

INT#

Interrupt Traps

A total of 32 interrupts by way of hardware and/or software are available.

ISCALE

Input Data-Scaling

Shifter

16 to 32-bit barrel left-shifter. ISCALE shifts incoming 16-bit data 0 to16 positions left, relative to the 32-bit

output within the fetch cycle; therefore, no cycle overhead is required for input scaling operations.

MPY

Multiplier

16

×

16-bit multiplier to a 32-bit product. MPY executes multiplication in a single cycle. MPY operates either

signed or unsigned 2s-complement arithmetic multiply.

MSTACK

Micro Stack

MSTACK provides temporary storage for the address of the next instruction to be fetched when program

address-generation logic is used to generate sequential addresses in data space.

MUX

Multiplexer

Multiplexes buses to a common input

NPAR

Next Program

Address Register

NPAR holds the program address to be driven out on the PAB on the next cycle.

OSCALE

Output

Data-Scaling

Shifter

16 to 32-bit barrel left-shifter. OSCALE shifts the 32-bit accumulator output 0 to 7 bits left for quantization

management and outputs either the 16-bit high- or low-half of the shifted 32-bit data to the Data-Write Data

Bus (DWEB).

PAR

Program Address

Register

PAR holds the address currently being driven on PAB for as many cycles as it takes to complete all memory

operations scheduled for the current bus cycle.

PC

Program Counter

PC increments the value from NPAR to provide sequential addresses for instruction-fetching and sequential

data-transfer operations.

PCTRL

Program

Controller

PCTRL decodes instruction, manages the pipeline, stores status, and decodes conditional operations.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320F206PZL | 16-Bit Digital Signal Processor |

| TMS320F240PQA | 16-Bit Microcontroller |

| TMS320C240PQL | 16-Bit Microcontroller |

| TMS320C240PQQ | 16-Bit Microcontroller |

| TMS320F240PQL | 16-Bit Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320F240PQ | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC 32B Dig Sig Cntrllr w/ Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F240PQA | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC 16B 5V fixed point DSP w/ Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F240PQG4 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC CMOS 320F240 BQFP TMS RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F240PQS | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC 32B Dig Sig Cntrllr w/ Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F241FN | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC 16B 5V fixed point DSP w/ Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。