- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300038 > TMS320LF2407APGEA (TEXAS INSTRUMENTS INC) 16-BIT, 20 MHz, OTHER DSP, PQFP144 PDF資料下載

參數(shù)資料

| 型號: | TMS320LF2407APGEA |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 16-BIT, 20 MHz, OTHER DSP, PQFP144 |

| 封裝: | GREEN, PLASTIC, LQFP-144 |

| 文件頁數(shù): | 67/134頁 |

| 文件大小: | 1724K |

| 代理商: | TMS320LF2407APGEA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當(dāng)前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁

TMS320LF2407A,TMS320LF2406A,TMS320LF2403A,TMS320LF2402A

TMS320LC2406A,TMS320LC2404A,TMS320LC2403A,TMS320LC2402A

DSP CONTROLLERS

SPRS145L JULY 2000 REVISED SEPTEMBER 2007

38

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

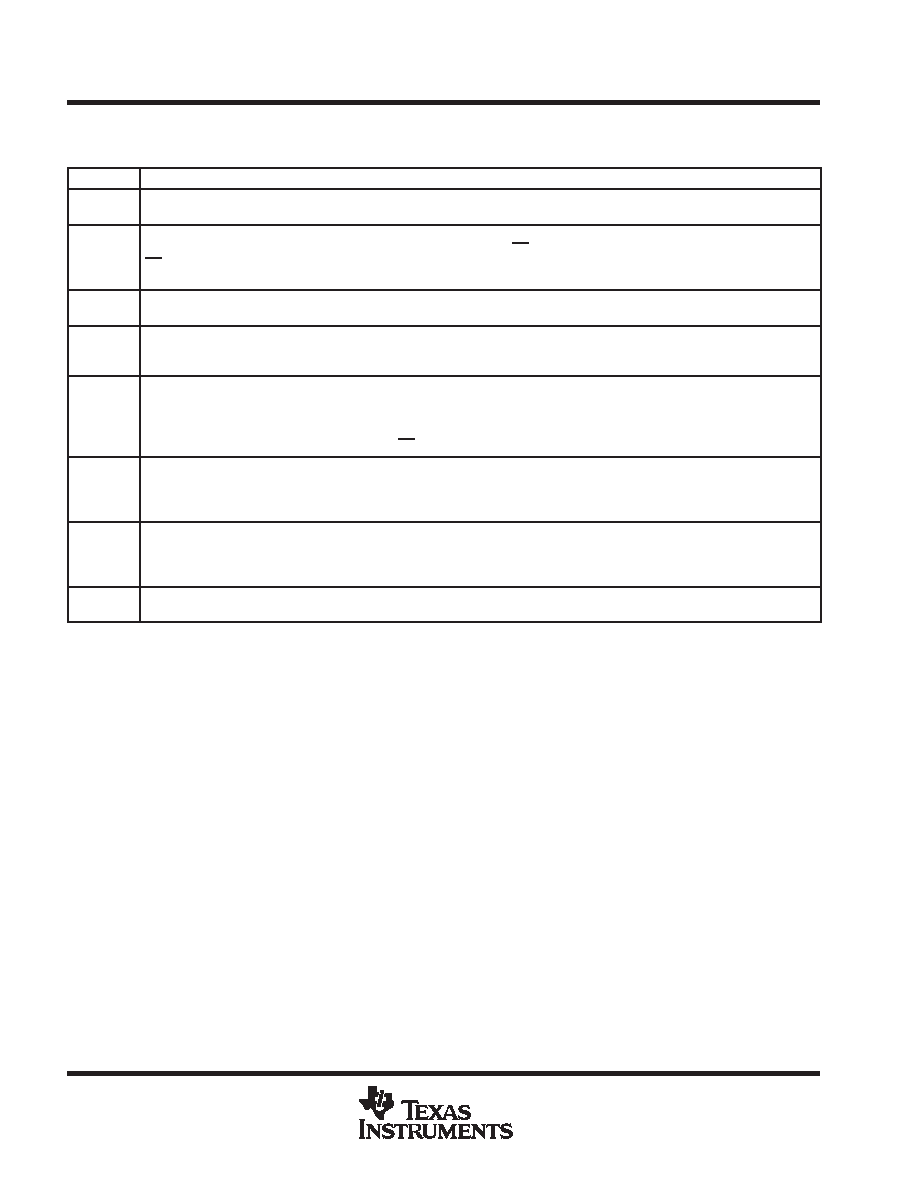

status and control registers (continued)

Table 5. Status Register Field Definitions (Continued)

FIELD

FUNCTION

DP

Data memory page pointer. The 9-bit DP register is concatenated with the 7 LSBs of an instruction word to form a direct memory

address of 16 bits. DP can be modified by the LST and LDP instructions.

INTM

Interrupt mode bit. When INTM is set to 0, all unmasked interrupts are enabled. When set to 1, all maskable interrupts are disabled.

INTM is set and reset by the SETC INTM and CLRC INTM instructions. RS also sets INTM. INTM has no effect on the unmaskable

RS and NMI interrupts. Note that INTM is unaffected by the LST instruction. This bit is set to 1 by reset. It is also set to 1 when

a maskable interrupt trap is taken.

OV

Overflow flag bit. As a latched overflow signal, OV is set to 1 when overflow occurs in the arithmetic logic unit (ALU). Once an

overflow occurs, the OV remains set until a reset, BCND/D on OV/NOV, or LST instruction clears OV.

OVM

Overflow mode bit. When OVM is set to 0, overflowed results overflow normally in the accumulator. When set to 1, the accumulator

is set to either its most positive or negative value upon encountering an overflow. The SETC and CLRC instructions set and reset

this bit, respectively. LST can also be used to modify the OVM.

PM

Product shift mode. If these two bits are 00, the multiplier’s 32-bit product is loaded into the ALU with no shift. If PM = 01, the PREG

output is left-shifted one place and loaded into the ALU, with the LSB zero-filled. If PM = 10, the PREG output is left-shifted by 4 bits

and loaded into the ALU, with the LSBs zero-filled. PM = 11 produces a right shift of 6 bits, sign-extended. Note that the PREG

contents remain unchanged. The shift takes place when transferring the contents of the PREG to the ALU. PM is loaded by the

SPM and LST #1 instructions. PM is cleared by RS.

SXM

Sign-extension mode bit. SXM = 1 produces sign extension on data as it is passed into the accumulator through the scaling shifter.

SXM = 0 suppresses sign extension. SXM does not affect the definitions of certain instructions; for example, the ADDS instruction

suppresses sign extension regardless of SXM. SXM is set by the SETC SXM instruction and reset by the CLRC SXM instruction

and can be loaded by the LST #1 instruction. SXM is set to 1 by reset.

TC

Test/control flag bit. TC is affected by the BIT, BITT, CMPR, LST #1, and NORM instructions. TC is set to a 1 if a bit tested by BIT

or BITT is a 1, if a compare condition tested by CMPR exists between AR (ARP) and AR0, if the exclusive-OR function of the 2 most

significant bits (MSBs) of the accumulator is true when tested by a NORM instruction. The conditional branch, call, and return

instructions can execute based on the condition of TC.

XF

XF pin status bit. XF indicates the state of the XF pin, a general-purpose output pin. XF is set by the SETC XF instruction and reset

by the CLRC XF instruction. XF is set to 1 by reset.

central processing unit

The TMS320x240xA central processing unit (CPU) contains a 16-bit scaling shifter, a 16 x 16-bit parallel

multiplier, a 32-bit central arithmetic logic unit (CALU), a 32-bit accumulator, and additional shifters at the

outputs of both the accumulator and the multiplier. This section describes the CPU components and their

functions. The functional block diagram shows the components of the CPU.

input scaling shifter

The TMS320x240xA provides a scaling shifter with a 16-bit input connected to the data bus and a 32-bit output

connected to the CALU. This shifter operates as part of the path of data coming from program or data space

to the CALU and requires no cycle overhead. It is used to align the 16-bit data coming from memory to the 32-bit

CALU. This is necessary for scaling arithmetic as well as aligning masks for logical operations.

The scaling shifter produces a left shift of 0 to 16 on the input data. The LSBs of the output are filled with zeros;

the MSBs can either be filled with zeros or sign-extended, depending upon the value of the SXM bit

(sign-extension mode) of status register ST1. The shift count is specified by a constant embedded in the

instruction word or by a value in TREG. The shift count in the instruction allows for specific scaling or alignment

operations specific to that point in the code. The TREG base shift allows the scaling factor to be adaptable to

the system’s performance.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS426409AP-60DJ | 4M X 4 EDO DRAM, 60 ns, PDSO24 |

| TMS426809AP-70DGC | 2M X 8 EDO DRAM, 70 ns, PDSO28 |

| TMS44400DJ-80 | 1M X 4 FAST PAGE DRAM, 80 ns, PDSO20 |

| TMS470R1B768PGEQR | 32-BIT, FLASH, 60 MHz, RISC MICROCONTROLLER, PQFP144 |

| TMS4C1050-4DJL | 256K X 4 OTHER FIFO, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320LF2407APGEA | 制造商:Texas Instruments 功能描述:16BIT DSP FLASH SMD 320LF2407 |

| TMS320LF2407APGEG4 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16-Bit Fixed-Pt DSP with Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320LF2407APGES | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16-Bit Univ Bus Drv With 3-State Outputs RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320LF2407PGES | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TMS320M640AGNZ4 | 制造商:Texas Instruments 功能描述:TMS320DM640 548PIN FCBGA PG2.0 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。