- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385942 > TNETA1611 (Texas Instruments, Inc.) STS-12c/STM-4 Receiver/Transimitter(STS-12C/STM-4接收/傳送器) PDF資料下載

參數(shù)資料

| 型號: | TNETA1611 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | STS-12c/STM-4 Receiver/Transimitter(STS-12C/STM-4接收/傳送器) |

| 中文描述: | STS-12c/STM-4接收器/ Transimitter(STS-12C/STM-4接收/傳送器) |

| 文件頁數(shù): | 4/9頁 |

| 文件大?。?/td> | 189K |

| 代理商: | TNETA1611 |

TNETA1611

STS-12c/STM-4 RECEIVER/TRANSMITTER

SDNS035E – AUGUST 1995 – REVISED JUNE 1996

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

bit alignment

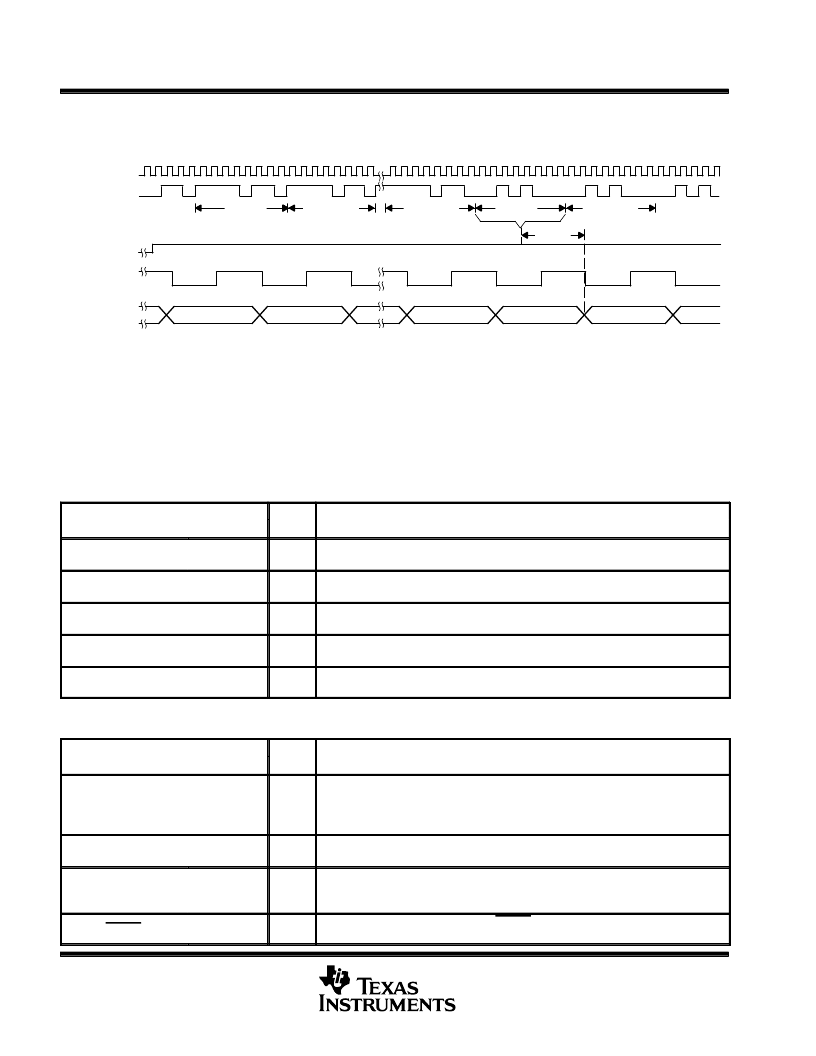

The bit-alignment function of the TNETA1611 is shown in Figure 1.

RSCT/RSCC

0

0

XX

XX (see Note B)

XX

XX

XX

XX

28 (first)

28

RSDT/RSDC

OOF

RPCK

RPD0–RPD7

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

First F6

Second F6

Twelfth F6

First 28

0

0

0

0

Second 28

Note A

NOTES: A. After the 12th contiguous F6 is detected, the bit alignment is adjusted so that the next eight bits (the first A2 byte) are grouped

together and sent out on RPD0–RPD7 after some delay time through the device.

B. Even when OOF is high, the TNETA1611 continues to convert the serial input data to parallel output data. While data is present at

the output, XX indicates that the alignment of the serial data into bytes on RPD0–RPD7 may not be known.

Figure 1. Bit Alignment

Terminal Functions

high-speed serial interface

TERMINAL

I/O

DESCRIPTION

NAME

NO.

RSCT, RSCC

3, 4

I

(PECL)

Receive serial clock (true and complement). RSCT and RSCC are a differential

622.08-MHz clock that accompanies the incoming serial data on RSDT and RSDC.

RSDT, RSDC

5, 6

I

(PECL)

Receive serial data (true and complement). RSDT and RSDC are differential data that

is accompanied by RSCT/RSCC. RSDT and RSDC are valid on the rising edge of RSCT.

TSCT, TSCC

20, 21

O

(PECL)

Transmit serial clock (true and complement). TSCT and TSCC are a differential

622.08-MHz clock that accompanies outgoing serial data on TSDT and TSDC.

TSDT, TSDC

16, 17

O

(PECL)

Transmit serial data (true and complement). TSDT and TSDC are differential data that

is valid on the rising edge of TSCT.

TXHCKT, TXHCKC

23, 24

I

(PECL)

Transmit high-speed clock (true and complement). TXHCKT and TXHCKC are a

differential 622.08-MHz clock source used when CLKLOOP is low.

control signals

TERMINAL

I/O

DESCRIPTION

NAME

NO.

CLKLOOP

29

I

(TTL)

Transmit clock-source loop. When CLKLOOP is low, TXHCKT and TXHCKC are used

for transmit operations. When CLKLOOP is high, the clock input with the receive data

stream is used for transmit operations. This clock is input differentially on RSCT and

RSCC.

FLB

30

I

(TTL)

Facility loopback. When FLB is high, the receive serial data and clock are looped back

to the transmit serial clock and data output.

OE

77

I

(TTL)

Output enable. OE enables or disables all TTL outputs. When OE is low, RPCK,

RPD0–RPD7, and TPCK are in the high-impedance state. When OE is high, these

terminals function normally.

RESET

44

I

(TTL)

Reset. The device is reset by taking RESET low. This action can result in the loss of

transmit or receive data that is being processed.

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TNETA1630 | 622.08-MHz Clock-Recovery Device(622.08-MHz時鐘發(fā)生裝置) |

| TO-252 | TO-252 (MP-3Z) |

| TODX2402 | FIBER OPTIC TRANSCEIVING MODULE |

| TOLD9321 | VLD Telchnical Data |

| TOLD9321F | VLD Telchnical Data |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1611PCA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Transceiver |

| TNETA1622 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:622.08-MHz CLOCK-RECOVERY DEVICE |

| TNETA1622DW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Clock/Data Recovery |

| TNETA1630DW | 制造商:Texas Instruments 功能描述: |

| TNETC400E-CM | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。