- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300041 > TPS54610QPWPRG4Q1 (TEXAS INSTRUMENTS INC) 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 PDF資料下載

參數(shù)資料

| 型號: | TPS54610QPWPRG4Q1 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 |

| 封裝: | GREEN, PLASTIC, HTSSOP-28 |

| 文件頁數(shù): | 8/22頁 |

| 文件大?。?/td> | 527K |

| 代理商: | TPS54610QPWPRG4Q1 |

www.ti.com

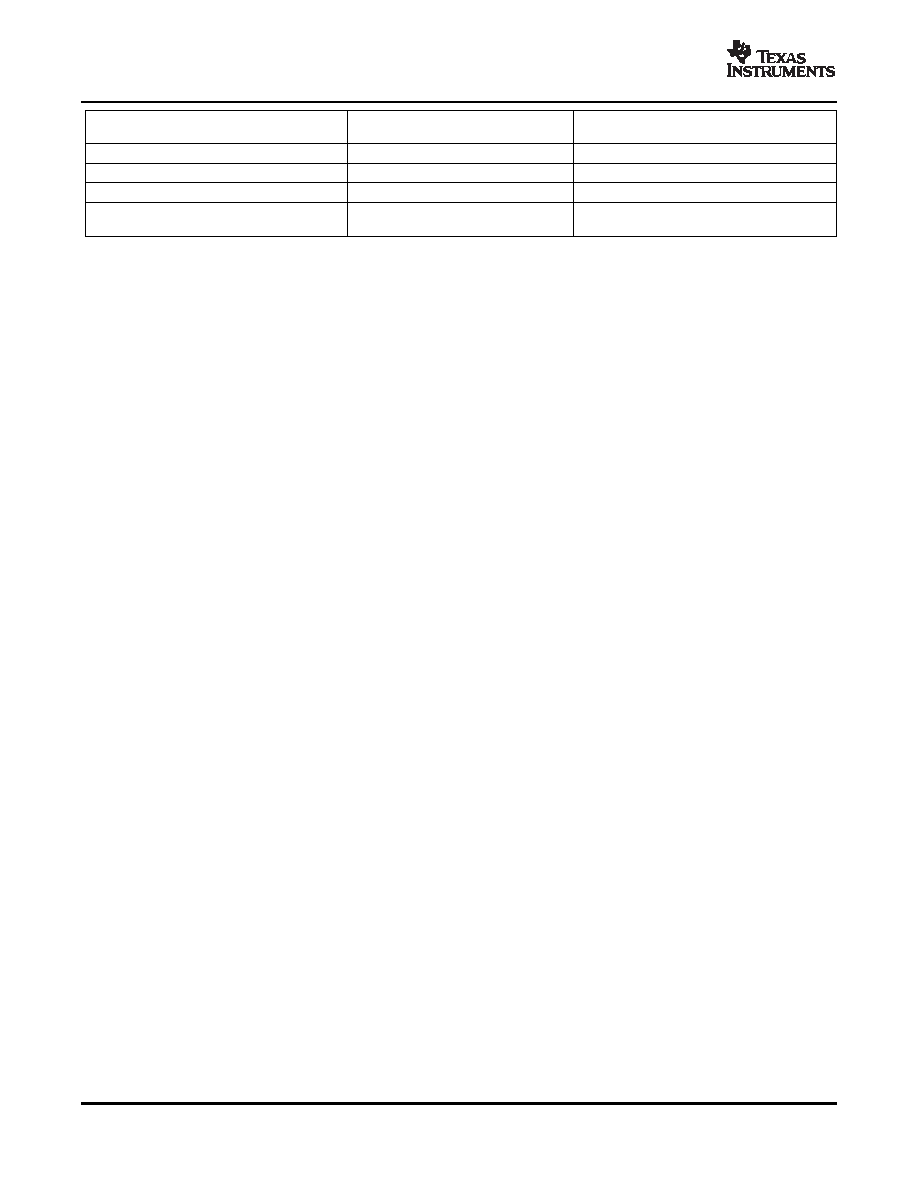

ERROR AMPLIFIER

PWM CONTROL

DEAD-TIME CONTROL AND MOSFET

OVERCURRENT PROTECTION

SLVS726 – JANUARY 2007

SWITCHING

SYNC PIN

RT PIN

FREQUENCY

350 kHz, internally set

Float or AGND

Float

550 kHz, internally set

≥ 2.5 V

Float

Externally set 280 kHz to 700 kHz

Float

R = 180 k

to 68 k

Externally synchronized frequency

Synchronization signal

R = RT value for 80% of external

synchronization frequency

on. The low-side FET remains on until the VSENSE

voltage decreases to a range that allows the PWM

comparator to change states. The TPS54610 is

The high-performance, wide-bandwidth, voltage-error

capable of sinking current continuously until the

amplifier sets the TPS54610 apart from most dc/dc

output reaches the regulation set-point.

converters. The user is given the flexibility to use a

If the current limit comparator trips for longer than

wide range of output L and C filter components to

100 ns, the PWM latch resets before the PWM ramp

suit the particular application needs. Type 2 or type 3

exceeds the error amplifier output. The high-side

compensation can be employed using external

FET turns off and low-side FET turns on to decrease

compensation components.

the energy in the output inductor and consequently

the output current. This process is repeated each

cycle in which the current limit comparator is tripped.

Signals from the error amplifier output, oscillator, and

current limit circuit are processed by the PWM

control logic. Referring to the internal block diagram,

DRIVERS

the control logic includes the PWM comparator, OR

Adaptive dead-time control prevents shoot-through

gate, PWM latch, and portions of the adaptive

current from flowing in both N-channel power

dead-time

and

control

logic

block.

During

MOSFETs during the switching transitions by actively

steady-state

operation

below

the

current

limit

controlling the turnon times of the MOSFET drivers.

threshold, the PWM comparator output and oscillator

The high-side driver does not turn on until the

pulse train alternately reset and set the PWM latch.

voltage at the gate of the low-side FET is below 2 V.

Once the PWM latch is reset, the low-side FET

While the low-side driver does not turn on until the

remains on for a minimum duration set by the

voltage at the gate of the high-side MOSFET is

oscillator pulse width. During this period, the PWM

below 2 V.

ramp discharges rapidly to its valley voltage. When

the ramp begins to charge back up, the low-side FET

The high-side and low-side drivers are designed with

turns off and high-side FET turns on. As the PWM

300-mA source and sink capability to quickly drive

ramp voltage exceeds the error amplifier output

the power MOSFETs gates. The low-side driver is

voltage, the PWM comparator resets the latch, thus

supplied from VIN, while the high-side drive is

turning off the high-side FET and turning on the

supplied from the BOOT pin. A bootstrap circuit uses

low-side FET. The low-side FET remains on until the

an external BOOT capacitor and an internal 2.5-

next oscillator pulse discharges the PWM ramp.

bootstrap switch connected between the VIN and

BOOT

pins.

The

integrated

bootstrap

switch

During transient conditions, the error amplifier output

improves drive efficiency and reduces external

could be below the PWM ramp valley voltage or

component count.

above the PWM peak voltage. If the error amplifier is

high, the PWM latch is never reset, and the high-side

FET remains on until the oscillator pulse signals the

control logic to turn the high-side FET off and the

The cycle-by-cycle current limiting is achieved by

low-side FET on. The device operates at

its

sensing the current flowing through the high-side

maximum duty cycle until the output voltage rises to

MOSFET and comparing this signal to a preset

the

regulation

set-point,

setting

VSENSE

to

overcurrent threshold. The high side MOSFET is

approximately the same voltage as VREF. If the

turned off within 200 ns of reaching the current limit

error amplifier output is low, the PWM latch is

threshold. A 100-ns leading edge blanking circuit

continually reset and the high-side FET does not turn

prevents current limit false tripping. Current limit

detection occurs only when current flows from VIN to

PH when sourcing current to the output filter. Load

protection during current sink operation is provided

by thermal shutdown.

16

相關PDF資料 |

PDF描述 |

|---|---|

| TPS62240DRVRG4 | 2.25 MHz 300 mA Step Down Converter in 2x2SON/TSOT23 Package |

| TPS62240DRVTG4 | 2.25 MHz 300 mA Step Down Converter in 2x2SON/TSOT23 Package |

| TPS62240DRVT | 2.25 MHz 300 mA Step Down Converter in 2x2SON/TSOT23 Package |

| TPS62242DRV | 2.25 MHz 300 mA Step Down Converter in 2x2SON/TSOT23 Package |

| TPS62242 | 2.25MHz 300mA Step-Down Converter in 2x2mm SON/TSOT23 Package |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TPS54610QPWPRQ1 | 制造商:Texas Instruments 功能描述:CONV DC-DC SGL-OUT STEP DOWN 28HTSSOP - Tape and Reel |

| TPS54611 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V TO 6-V INPUT, 6-A OUTPUT SYNCHRONOUS BUCK PWM SWITCHER WITH INTEGRATED FETs |

| TPS54611-EP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V TO 6-V INPUT, 6-A OUTPUT SYNCHRONOUS BUCK PWM SWITCHER WITH INTEGRATED FETs (SWIFTa?¢) |

| TPS54611PWP | 功能描述:直流/直流開關調(diào)節(jié)器 Lo-In Voltage 6A Sync Buck Converter RoHS:否 制造商:International Rectifier 最大輸入電壓:21 V 開關頻率:1.5 MHz 輸出電壓:0.5 V to 0.86 V 輸出電流:4 A 輸出端數(shù)量: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:PQFN 4 x 5 |

| TPS54611PWPG4 | 功能描述:直流/直流開關調(diào)節(jié)器 Lo-In Voltage 6A Sync Buck Converter RoHS:否 制造商:International Rectifier 最大輸入電壓:21 V 開關頻率:1.5 MHz 輸出電壓:0.5 V to 0.86 V 輸出電流:4 A 輸出端數(shù)量: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:PQFN 4 x 5 |

發(fā)布緊急采購,3分鐘左右您將得到回復。