- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373685 > TQ8101C (TriQuint Semiconductor,Inc.) CONNECTOR ACCESSORY PDF資料下載

參數(shù)資料

| 型號: | TQ8101C |

| 廠商: | TriQuint Semiconductor,Inc. |

| 英文描述: | CONNECTOR ACCESSORY |

| 中文描述: | 連接器附件 |

| 文件頁數(shù): | 3/14頁 |

| 文件大小: | 227K |

| 代理商: | TQ8101C |

TQ8101C

T

P

3

For additional information and latest specifications, see our website:

www.triquint.com

Functional Description

Figure 2 shows a block diagram of the TQ8101C

multiplexer, demultiplexer, framer, and PLL clock

synthesizer (MDFP). The primary purpose of TQ8101C

is to integrate the conversion of serial and parallel

SONET/SDH data with bit alignment and clock

synthesis in a single device.

Multiplexing

Byte-wide input data on MXDT(7:0)

1

is continuously

strobed into the multiplexer on the rising edge of the

multiplexer clock output, MXCK(2:0).

2

Any of these

three MXCK pins may be used as a reference point for

relative timing. (See Table8 for setup, hold, and skew

times. See Table1 for clock selection options.)

Either an on-chip synthesized clock (see “PLL Clock

Synthesis”) or an external high-speed multiplexer

Notes:

1. MXDT(0) is defined as the least significant bit.

2. MXCK(2:0) nominally runs at 77.76 MHz in STS-12/STM-4 mode,

and at 19.44 MHz in STS-3/STM-1 mode.

3. Internal signal. See Figure 5, "TQ8101C Loopback Modes."

4. DXDT (0) is defined as the least significant bit.

Frame Detection

and Recovery

Shift

Register

Parallel

Register

1/3

1/8

1/2

1/2

1/3

Mux

DXDTIN

DXHSCK

XFD

OOF

RT

DXDT(7:0)

DXSYNC

DXCK

DXRCK

clock, MXHC, serializes the input data bytes. In the

normal mode of operation, the serial data is then

buffered as ECL-compatible output on TXDT. An ECL

output is provided for the transmit clock, TXCK.

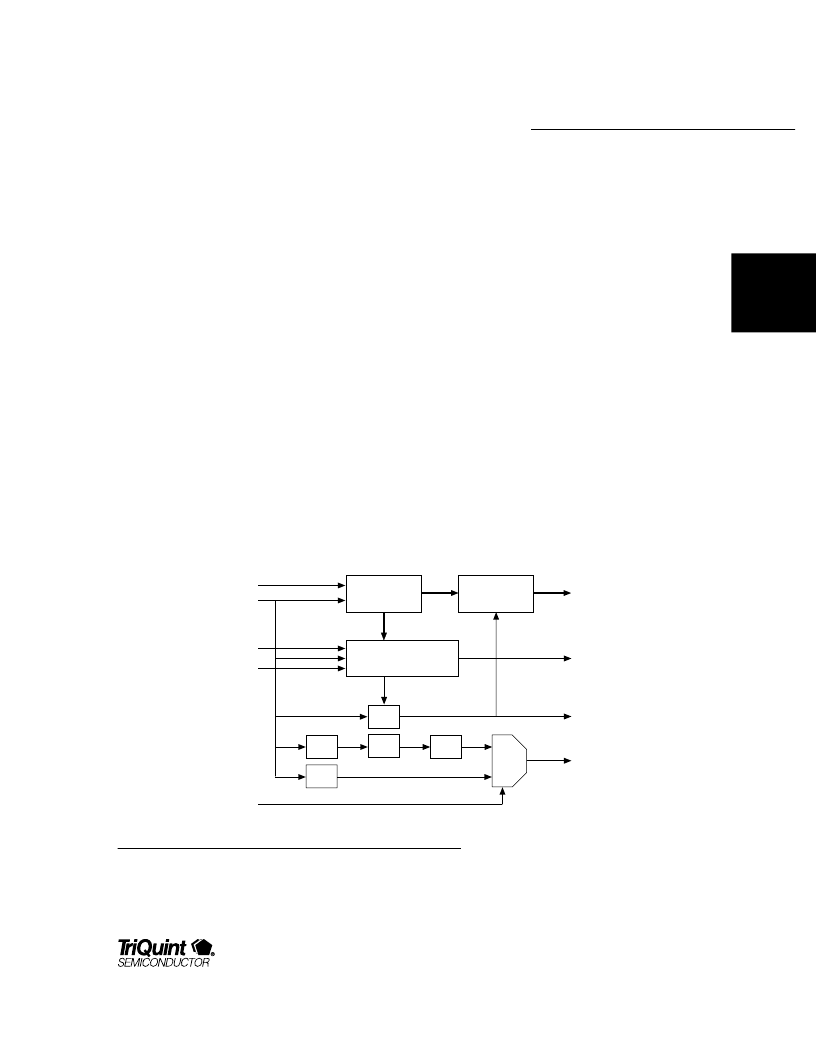

Demultiplexing

As shown in Figure 4, The demultiplexer block converts

incoming serial data on DXDTIN

3

. Byte-wide output

data is presented on DXDT(7:0)

4

slightly after the

falling edge of the output demultiplexer clock, DXCK.

(See Table8 for setup, hold, and skew times.)

The demultiplexer block also includes clock divider

circuitry, which is used by the demultiplexer to control

divide-by-8 output on DXCK. The MDFP provides a

divide-by-3 or divide-by-12 output, DXRCK.

(See Table 1 for mode selection options.)

Figure 4. Demultiplexer Functional Block

相關PDF資料 |

PDF描述 |

|---|---|

| TQ8103 | 622 Mb/s Clock & Data Recovery |

| TQ8105 | SONET/SDH Transceivers |

| TQ8106 | SONET/SDH Transceivers |

| TQ8213 | Multiplexer |

| TQ9132B | 3V Cellular TDMA/AMPS Power Amplifier IC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TQ8101C-M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM Processor |

| TQ8103 | 制造商:TRIQUINT 制造商全稱:TriQuint Semiconductor 功能描述:622 Mb/s Clock & Data Recovery |

| TQ8103-Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Clock/Data Recovery |

| TQ8105 | 制造商:TRIQUINT 制造商全稱:TriQuint Semiconductor 功能描述:SONET/SDH Transceivers |

| TQ8106 | 制造商:TRIQUINT 制造商全稱:TriQuint Semiconductor 功能描述:SONET/SDH Transceivers |

發(fā)布緊急采購,3分鐘左右您將得到回復。