- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373714 > TS68302DESC01QYA (ATMEL CORP) Integrated Multiprotocol Processor IMP PDF資料下載

參數(shù)資料

| 型號(hào): | TS68302DESC01QYA |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | Integrated Multiprotocol Processor IMP |

| 中文描述: | 16-BIT, 16.67 MHz, RISC MICROCONTROLLER, CQFP132 |

| 封裝: | CERAMIC, QFP-132 |

| 文件頁(yè)數(shù): | 14/47頁(yè) |

| 文件大?。?/td> | 1149K |

| 代理商: | TS68302DESC01QYA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

14

TS68302

2117A–HIREL–11/02

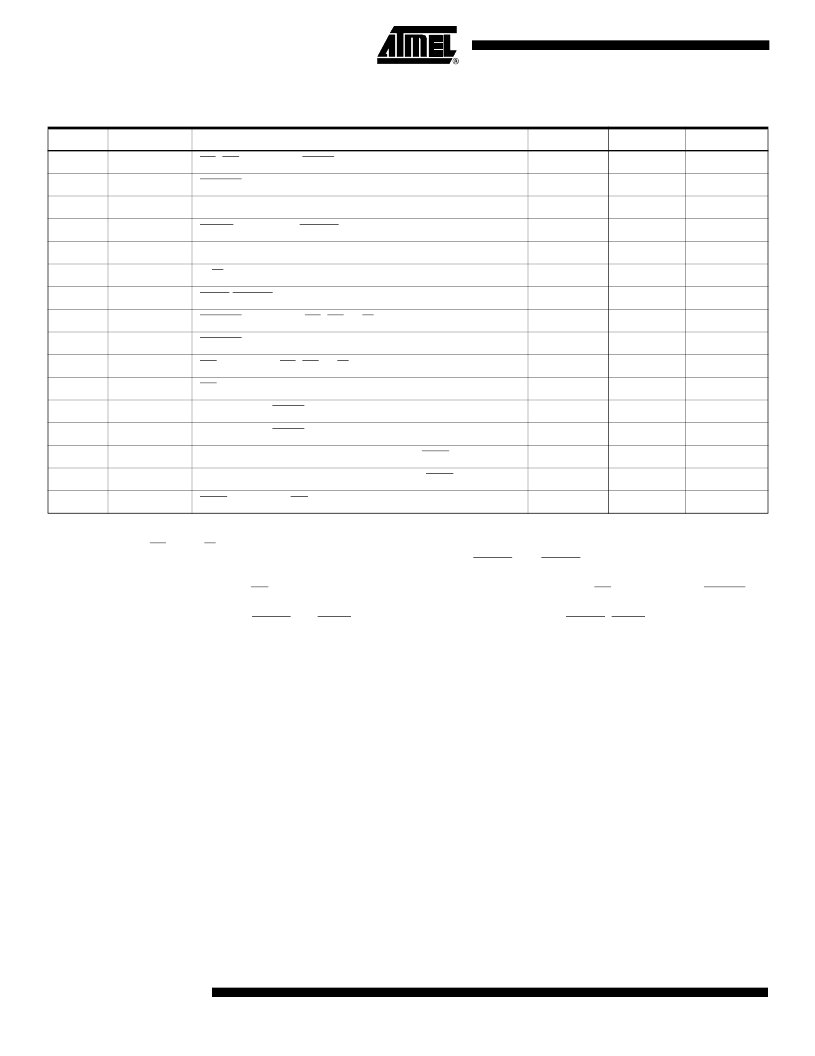

Notes:

1. For loading capacitance of less than or equal to 50 pF, subtract 4 ns from the value given in the maximum columns.

2. Actual value depends on clock period.

3. When AS and R/W are equally loaded (±20%), subtract 5 ns from the values given in these columns.

4. If the asynchronous input setup (#47) requirement is satisfied for DTACK, the DTACK asserted to data setup time (#31)

requirement can be ignored. The data must only satisfy the data-in to clock low setup time (#27) for the following clock cycle.

5. The TS68302 will negate BG and begin driving the bus if external arbitration logic negates BR before asserting BGACK.

6. The minimum value must be met to guarantee proper operation. If the maximum value is exceeded, BG may be reasserted.

7. If #47 is satisfied for both DTACK and BERR, #48 may be ignored. In the absence of DTACK, BERR is a synchronous input

using the asynchronous input setup time (#47).

8. For power-up, the TS68302 must be held in the reset state for 100 ms to allow stabilization of on-chip circuit. After the sys-

tem is powered up #56 refers to the minimum pulse width required to reset the processor.

9. Occurs on S0 of SDMA read/write access when the SDMA becomes bus master.

10. This specification is valid only when the RMCST bit is set in the SCR register.

44

t

SHVPH

AS, DS negated to AVEC negated

0

50

ns

46

t

GAL

BGACK width low

1.5

clks

47

t

ASI

Asynchronous input setup time

(4)

10

ns

48

t

BELDAL

BERR asserted to DTACK asserted

(2)(7)

10

ns

53

t

CHDOI

Data-out hold from clock high

0

ns

55

t

RLDBD

R/W asserted to data bus impedance change

0

ns

56

t

HRPW

HALT/RESET pulse width

(8)

10

clks

57

t

GASD

BGACK negated to AS, DS, R/W driven

1.5

clks

57A

t

GAFD

BGACK negated to FC

1

clks

58

f

RHSD

BR negated to AS, DS, R/W driven

(5)

1.5

clks

58A

t

RHFD

BR negated to FC

(5)

1

clks

60

t

CHBCL

Clock high to BCLR asserted

30

ns

61

t

CHBCH

Clock high to BCLR negated

(9)

30

ns

62

t

CLRML

Clock low (S0 falling edge during read) to RMC asserted

30

ns

63

t

CHRMH

Clock high (S7 rising edge during write) to RMC negated

30

ns

64

t

RMHGL

RMC negated to BG asserted

(10)

30

ns

Table 8.

AC Electrical Specifications

IMP Bus Master Cycles (see Figure 7, Figure 8 and Figure 9) f = 16.67 MHz (Continued)

Num.

Symbol

Parameter

Min

Max

Unit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS68302VA16 | Integrated Multiprotocol Processor IMP |

| TS68302 | Integrated Multiprotocol Processor IMP |

| TS68302MR16 | Integrated Multiprotocol Processor IMP |

| TS68302VR16 | Integrated Multiprotocol Processor IMP |

| TS68302MA16 | CABLE ASSEMBLY; LEAD-FREE SOLDER; MINI UHF MALE TO SMA MALE; 50 OHM, RG58C/U COAX; 12" CABLE LENGTH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS68302MA16 | 制造商:e2v technologies 功能描述:68302 INTEGRATED MULTI-PROTOCOL PROCESSOR - 16MHZ, 5.0V, CQFP, MIL TEMP 制造商:e2v technologies 功能描述:MPU TS68000 RISC 16BIT HCMOS 16MHZ 132CQFP - Trays |

| TS68302MA1B/C16 | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:Integrated Multiprotocol Processor IMP |

| TS68302MA1B/T16 | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:Integrated Multiprotocol Processor IMP |

| TS68302MAB/C16 | 制造商:e2v technologies 功能描述:MPU TS68000 RISC 16BIT HCMOS 16.67MHZ 132CQFP - Trays 制造商:e2v technologies 功能描述:TS68302MAB/C16 - Trays |

| TS68302MR1-16 | 制造商:e2v technologies 功能描述:TS68302MR1-16 - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。