- 您現在的位置:買賣IC網 > PDF目錄365987 > TSPC106AVGS66CE MEMORY CONTROLLER PDF資料下載

參數資料

| 型號: | TSPC106AVGS66CE |

| 英文描述: | MEMORY CONTROLLER |

| 中文描述: | 內存控制器 |

| 文件頁數: | 15/40頁 |

| 文件大小: | 569K |

| 代理商: | TSPC106AVGS66CE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

15

TSPC106

2102B

–

HIREL

–

02/02

Memory Interface

Signals

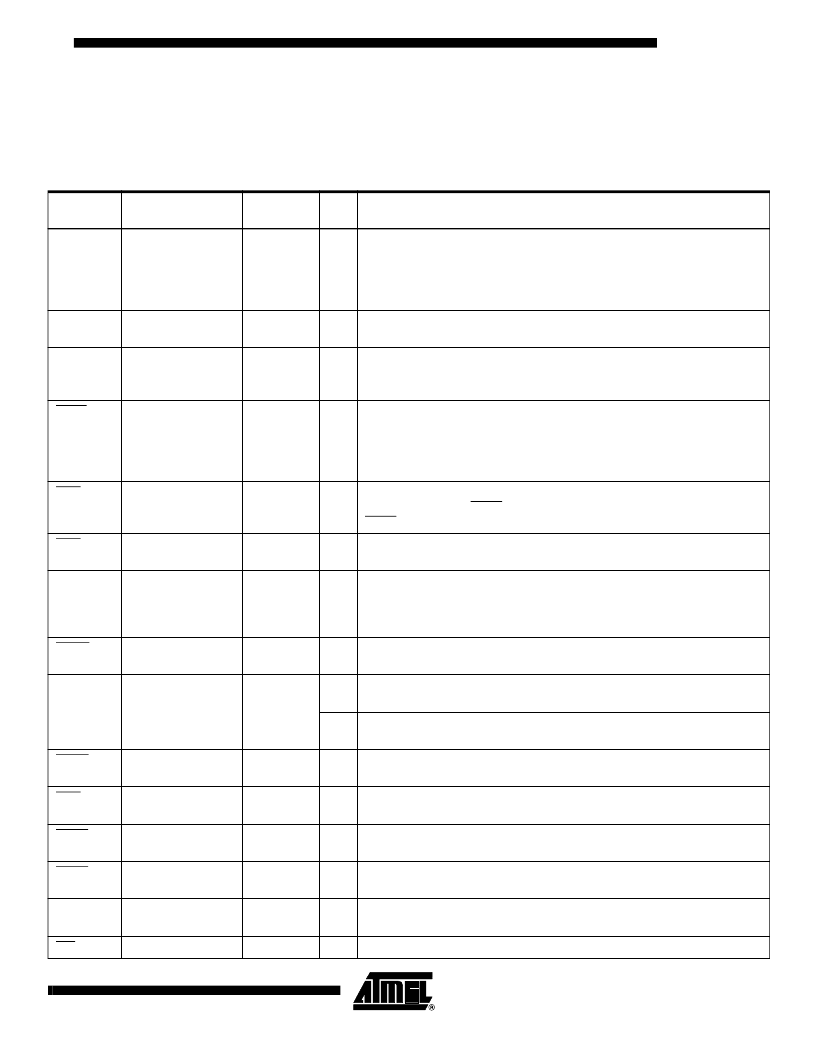

Table 6 lists the memory interface signals and provides a brief description of their func-

tions. The memory interface supports either standard DRAMs or EDO DRAMs, and

either standard ROMs or Flash ROMs. Some of the memory interface signals perform

different functions depending on the RAM and ROM configurations.

Table 6.

Memory Interface Signals

Signal

Signal Name

Numberof

Pins

I/O

Signal Description

AR0

MA0

ROM address 0

8

O

Represents address bit 0 of the 8-bit ROM/Flash. Note that AR0 is only

supported for ROM bank 0 when configured for an 8-bit ROM/Flash data

bus width. The extra address bit allows for up to 2 Mbytes of ROM when

using the 8-bit wide data path. Bits 1 - 8 of the ROM address are provided

by AR[1:8] and bits 9 - 20 of the ROM address are provided by AR[9:20].

AR[1:8]

PAR[0:7]

ROM address 1 - 8

8

O

Represents bits 1 - 8 of the ROM/Flash address. The other ROM address

bits are provided by AR0 and AR[9:20].

AR[9:20]

MA[1:12]

ROM address

9 - 20

12

O

Represents bits 9 - 20 of the ROM/Flash address (the 12 lowest order bits,

with AR20 as the least significant bit (lsb)). Bits 0 - 8 of the ROM address

are provided by AR0 and AR[1:8].

BCTL[0:1]

Buffer control 0 - 1

2

O

Used to control external data bus buffers (directional control and high-

impedance state) between the 60x bus and memory. Note that external

data buffers may be optional for lightly loaded data buses, but buffers are

required whenever an L2 cache and ROM/Flash (on the 60x/memory bus)

are both in the system or when ECC is used.

CAS[0:7]

Column address

strobe 0 - 7

8

O

Indicates a memory column address is valid and selects one of the

columns in the row. CAS0 connects to the most significant byte select.

CAS7 connects to the least significant byte select.

FOE

Flash output

enable

1

O

Enables Flash output for the current read access.

MA0

MA[1:12]

AR0

AR[9:20]

Memory address

0 - 12

13

O

Represents the row/column multiplexed physical address for DRAMs or

EDOs (MA0 is the most significant address bit; MA12 is the least significant

address bit). Note that MA0 also functions as the ROM address signal AR0

and MA[1:12] function as the ROM address signals AR[9:20].

MDLE

Memory data latch

enable

1

O

Enables the external, latched data buffer for read operations, if such a

buffer is used in the system.

PAR[0:7]

AR[1:8]

Data parity/ECC

8

O

Represents the byte parity or ECC being written to memory (PAR0 is the

most significant bit).

I

Represents the byte parity or ECC being read from memory (PAR0 is the

most significant bit).

PPEN

Parity path read

enable

1

O

Enables external parity/ECC bus buffer or latch for memory read

operations.

RAS[0:7]

Row address

strobe 0 - 7

8

O

Indicates a memory row address is valid and selects one of the rows in the

bank.

RCS0

ROM/Flash bank 0

select

1

O

Selects ROM/Flash bank 0 for a read access or Flash bank 0 for a read or

write access.

RCS1

ROM/Flash bank 1

select

1

O

Selects ROM/Flash bank 1 for a read access or Flash bank 1 for a read or

write access.

RTC

Real-time clock

1

I

External clock source for the memory refresh logic when the TSPC106 is in

the suspend power-saving mode.

WE

Write enable

1

O

Enables writing to DRAM, EDO or Flash.

相關PDF資料 |

PDF描述 |

|---|---|

| TSPC106AVGS66CG | MEMORY CONTROLLER |

| TSPC106AVGS83CE | MEMORY CONTROLLER |

| TSPC106AVGS83CG | MEMORY CONTROLLER |

| TSPC106AVGSU66CE | MEMORY CONTROLLER |

| TSPC106AVGSU66CG | MEMORY CONTROLLER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSPC106AVGS66CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGS83CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGS83CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGSU/T66CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGSU/T66CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復。