- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365987 > TSPC106AVGU83CG MEMORY CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | TSPC106AVGU83CG |

| 英文描述: | MEMORY CONTROLLER |

| 中文描述: | 內(nèi)存控制器 |

| 文件頁(yè)數(shù): | 31/40頁(yè) |

| 文件大?。?/td> | 569K |

| 代理商: | TSPC106AVGU83CG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

31

TSPC106

2102B

–

HIREL

–

02/02

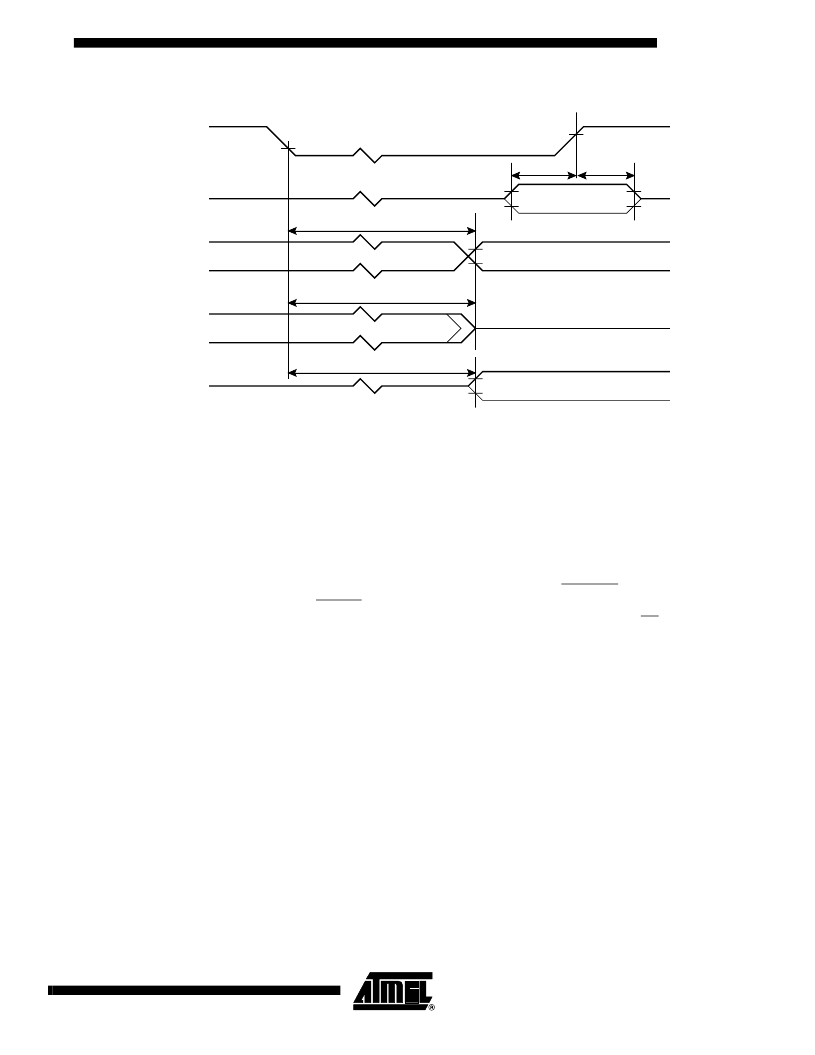

Figure 14.

Test Access Port Timing Diagram

Architectural

Overview

60x Processor Interface

The TSPC106 supports a programmable interface to a variety of PowerPC microproces-

sors operating at select bus speeds.The address bus is 32 bits wide and the data bus is

64 bits wide. The 60x processor interface of the TSPC106 uses a subset of the 60x bus

protocol, supporting single-beat and burst data transfers. The address and data buses

are decoupled to support pipelined transactions.

Two signals on the TSPC106, local bus slave claim (LBCLAIM) and data bus grant local

bus slave (DBGLB), are provided for an optional local bus slave. However, the local bus

slave must be capable of generating the transfer acknowledge (TA) signal to interact

with the 60x processor(s).

Depending on the system implementation, the processor bus may operate at the PCI

bus clock rate or at two or three times the PCI bus clock rate. The 60x processor bus is

synchronous with all timing relative to the rising edge of the 60x bus clock.

Secondary (L2)

Cache/Multiple

Processor Interface

The 106 provides support for the following configurations of 60x processors and L2

cache:

Up to four 60x processors with no L2 cache

A single 60x processor plus a direct-mapped, lookaside, L2 cache using the internal

L2 cache controller of the TSPC106

Up to four 60x processors plus an externally-controlled L2 cache

The internal L2 cache controller generates the arbitration and support signals necessary

to maintain a write-through or write-back L2 cache. The internal L2 cache controller sup-

ports either asynchronous SRAMs, pipelined burst SRAMs or synchronous burst

SRAMs, using byte parity for data error detection.

TCK

12

12

13

Input Data Valid

Output Data Valid

Output Data Valid

10

11

TDI, TMS

TDO

TDO

TDO

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPC106AMG66CE | MEMORY CONTROLLER |

| TSPC106AMG66CG | MEMORY CONTROLLER |

| TSPC106AMG83CE | MEMORY CONTROLLER |

| TSPC106AMG83CG | MEMORY CONTROLLER |

| TSPC106AVG66CE | MEMORY CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC120-124 | 制造商:Traco Power 功能描述:AC-DC CONV, DIN RAIL, 1 O/P, 120W, 5A, 24V; Power Supply Output Type:Adjustable, Fixed; Input Voltage VAC:85V to 132V, 187V to 264V; No. of Outputs:1; Output Voltage Nom.:24V; Output Current Max:5A; Output Power Max:120W ;RoHS Compliant: Yes 制造商:Traco Power 功能描述:DIN Rail PSU 24Vdc, 120W, 5A |

| TSPC240-124 | 制造商:Traco Power 功能描述:AC-DC CONV, DIN RAIL, 1 O/P, 240W, 10A, 24V; Power Supply Output Type:Adjustable, Fixed; Input Voltage VAC:85V to 132V, 187V to 264V; No. of Outputs:1; Output Voltage Nom.:24V; Output Current Max:10A; Output Power Max:240W ;RoHS Compliant: Yes 制造商:Traco Power 功能描述:DIN Rail PSU 24Vdc, 240W, 10A |

| TSPC480-124 | 制造商:Traco Power 功能描述:AC-DC CONV, DIN RAIL, 1 O/P, 480W, 20A, 24V; Power Supply Output Type:Adjustable, Fixed; Input Voltage VAC:85V to 132V, 187V to 264V; No. of Outputs:1; Output Voltage Nom.:24V; Output Current Max:20A; Output Power Max:480W ;RoHS Compliant: Yes 制造商:Traco Power 功能描述:DIN Rail PSU 24Vdc, 480W, 20A |

| TSPC603EMA5L | 制造商:e2v 功能描述: 制造商:e2v technologies 功能描述: |

| TSPC603EVA5L | 制造商:e2v technologies 功能描述:TSPC603EVA5L - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。