- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385951 > TVP3703FN (Texas Instruments, Inc.) VIDEO INTERFACE PALETTE TRUE-COLOR CMOS RAMDAC PDF資料下載

參數(shù)資料

| 型號: | TVP3703FN |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | VIDEO INTERFACE PALETTE TRUE-COLOR CMOS RAMDAC |

| 中文描述: | VIDEO接口調(diào)色板真彩色的CMOS的RAMDAC |

| 文件頁數(shù): | 7/21頁 |

| 文件大小: | 298K |

| 代理商: | TVP3703FN |

TVP3703

VIDEO INTERFACE PALETTE

TRUE-COLOR CMOS RAMDAC

SLAS100 – MARCH 1996

7

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

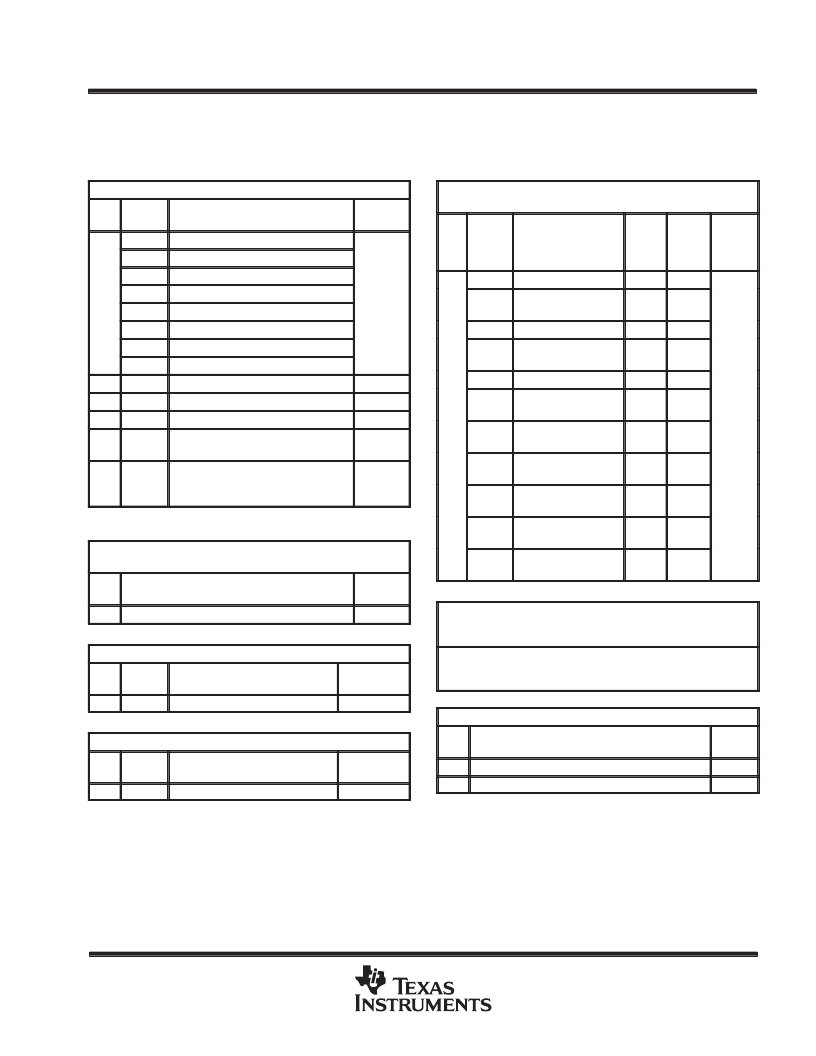

register content descriptions

A write to any register containing reserved bits should always write 0s to the reserved bits (the exception being

bit 7 of power management register A). On reads, all reserved bits should be masked out.

The values of register bits that are reset on power-up are listed in the reset value columns below.

PIXEL COMMAND REGISTER (RS0–RS2 = 110)

BIT

VALUE

FUNCTION

RESET

VALUE

000

8-bit color

001

Reserved

010

Reserved

7 5

7–5

011

Reserved

000

100

Reserved

101

15-bit direct color

110

16-bit direct color

111

24-bit direct color

4

1 = Enable extended register space

0

3

1 = Enable extended pixel modes

1 = Add 7.5 IRE blanking pedestal

0

2

0

1

1 = Micro port interface to RAM is

8-bit not 6-bit

0

0

1 = Sleep mode (micro port and

palette RAM still enabled, see power

management features section)

Institute of Radio Engineers

0

INDEX LOW AND HIGH BYTE REGISTERS

(RS0–RS2 = 100, RS0–RS2 = 111)

BIT

FUNCTION

RESET

VALUE

7–0

Low/high byte of 16-bit index

0

COMPANY ID REGISTER (Index 0000h)

BIT

VALUE

FUNCTION

RESET

VALUE

7–0

97h

Texas Instruments

Read only

DEVICE ID REGISTER (Index 0001h)

BIT

VALUE

FUNCTION

RESET

VALUE

7–0

03h

TVP3703

Read only

PIXEL MODE SELECT REGISTERS

(Primary and Secondary) (Indexes 0003h, 0004h)

BIT

VALUE

FUNCTION

MAX

PCLK

(MHz)

MAX

VIDEO

RATE

(MHz)

110

RESET

VALUE

00h

8-bit indexed color

110

01h

15-bit direct color or

8-bit indexed color

110

110

02h

15-bit direct color

110

110

03h

16-bit 5–6–5 direct

color

110

110

04h

24-bit direct color

110

55

05h

Double 8-bit indexed

color

67.5

135

Not

Reset

7–0

06h

16-bit 5–6–5 direct

color (2

×

8-bit input)

110

55

07h

8-bit indexed color

(2

×

4-bit input)

110

55

08h

15-bit direct color

(2

×

4-bit input)

110

55

09h

Double 24-bit direct

color

85

56.5

0Ah–

FFh

Reserved

PIPELINE TIMING CONTROL REGISTER

(Double 8-bit and 24-bit modes only)

(Index 0005h)

The TVP3703 uses an internal PLL and timing control circuitry to

automatically adjust pipeline. There are no register bits to program,

since the device accounts for all desired frequency ranges.

SOFT RESET REGISTER (Index 0006h)

BIT

FUNCTION

RESET

VALUE

7–1

Reserved

0

0

1 = Reset all registers to power-on default state

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TVP5020TQFP | NTSC/PAL VIDEO DECODER |

| TVP5031 | NTSC/PAL VIDEO DECODER |

| TVP5031TQFP | NTSC/PAL VIDEO DECODER |

| TVP5031CPFP | Color Decoder Circuit |

| TVR4J | TOSHIBA Fast Recovery Diode Silicon Diffused Type High Speed Rectifier Applications (fast recovery) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TVP4020AGFN | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TVP4020AGFN-8 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TVP5010 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:NTSC/PAL Video Decoder |

| TVP5010CPFP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TVP5020 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:NTSC/PAL VIDEO DECODER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。