- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98307 > TZA1047HL/M3 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | TZA1047HL/M3 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1.4 MM HEIGHT, PLASTIC, MS-026, SOT314-2, LQFP-64 |

| 文件頁數(shù): | 28/69頁 |

| 文件大小: | 324K |

| 代理商: | TZA1047HL/M3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

9397 750 14664

Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 02 — 1 June 2005

34 of 69

Philips Semiconductors

TZA1047

Preprocessor IC for CD and DVD rewritable

If bit RFCAL = 1, output XDN provides an amplied, low-pass ltered version of signal

rf-cal (see Section 7.6). This can be used to eliminate the offset in the RF path.

Note that the rf-cal output is unipolar, so only positive outputs are possible. If bit

Q/NE = 0, signal XDN (or rf-cal) is output at pin S2.

The relationship between the XDN signal components is shown in Table 18.

Calculation of XDN gain: In TZA1047/M1 XDN was a voltage output on a 1.3 V bias level,

made with a conversion resistance of 80 k

. This was connected to S2 on centaurus1

with a 100 series resistor. The reference voltage on S2 was set to 1.2 V. With a second

resistor, a bias current was added to have a 6

A bias level. (S2 is a 12 A range unipolar

input).

This situation resulted in a full range (6

A) swing with IN3 = 0h so Idoc3 = 16 A.

Calculating back, the modulation on XDN is (6

A × 80/100)/16 A = 30 %. This is more

than expected but will be accepted as a fact of life.

Intermezzo: XDN is used to measure lens position. The beam is 3.5 mm diameter through

the lens, the position shift range required is 0.4mm. This is 11.5 %, but XDN will not be

linear with position because the beam intensity in the middle is higher than at the edges.

Calculation for TZA1047/M2: Assume 30 % modulation. XDN will be connected to D2, a

bipolar input with

±12 A range. The nominal reference current should be

12

× (1/0.3) = 40 A. By using I

N3 =4+4 × IN3, this is achieved at IN3 = 9h which is nicely

in the middle of the range.

7.11.5 Track loss servo signal block (normalizer sub-block)

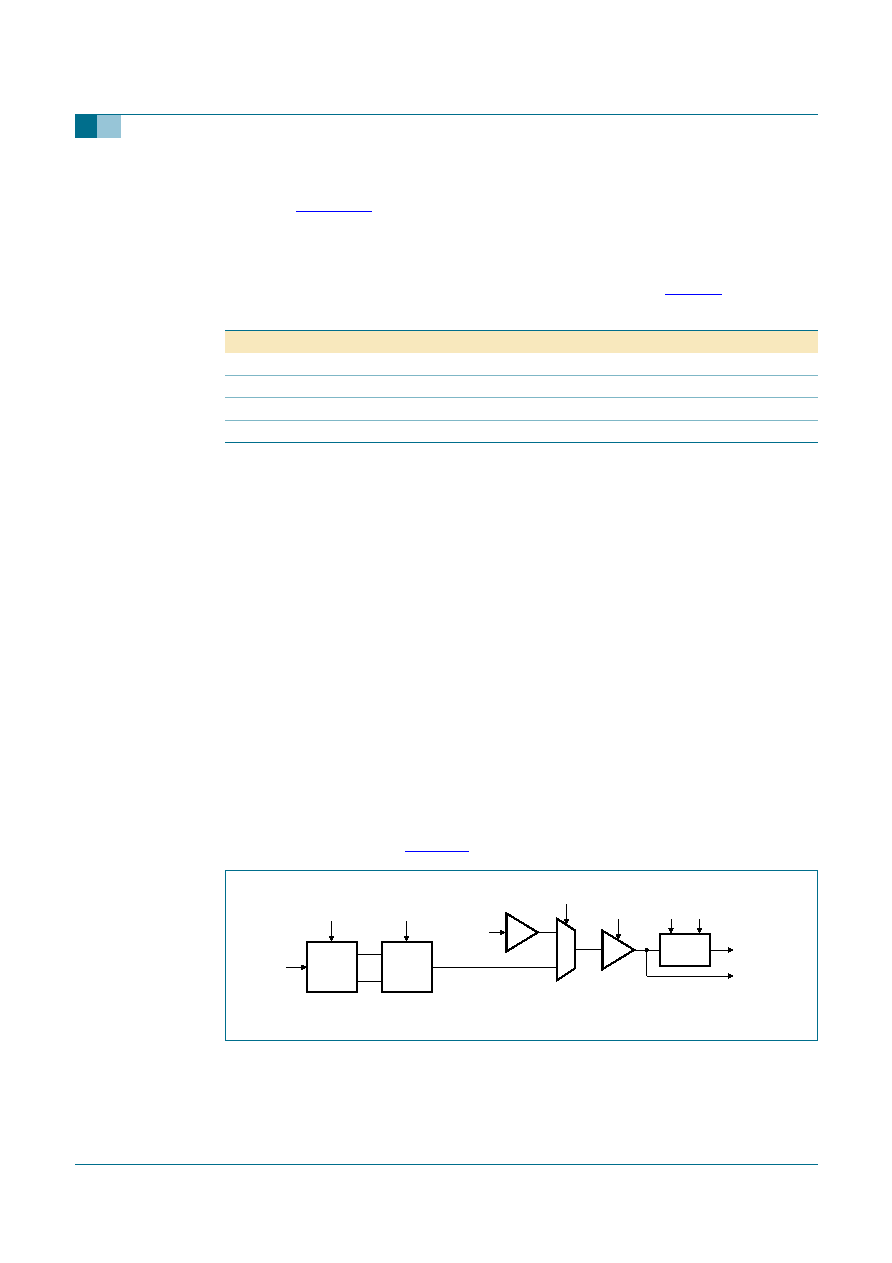

The TL block produces a normalized track loss error signal TLN. A detailed block diagram

of the TL block is shown in Figure 19.

If bit RTLN = 1, signal TLN is only valid for the tracking methods 3-spot CA and 3-spot PP.

If bit RTLN = 0, signal TLN is the low-pass ltered central sum signal QS, scaled with a

factor of 1

3.

Table 18:

XDN signal (bit PXDN = 0)

Bit S4/8

Bit CA/PP

Bit RFCAL

Signal XDN

0

N[Q5, Q6]

× GDOC × IN3

X

1

0

N[(Q1 + Q3), (Q2 + Q4)]

× G

DOC × IN3

1

0

N[(Q1 + Q3 + Q5), (Q2 + Q4 + Q6)]

× G

DOC × IN3

X

1

rfcal

Fig 19. TL block.

001aab191

+/

PTLN

N

IDOC4

CLAMP

CA/PP

Q5, Q6,

Qsnorm

QSNORM

TLN

TLN to MON

RTLN

CLMP ICL

1/3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TZA1049TH | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 1N5376ATR | TRANS PNP HV -300V -500MA TO-92 |

| 1N5376BTR | TRANS PNP HV -200V -1000MA TO-92 |

| 1N5376C | TRANS PNP HG -15V -3000MA TO-92 |

| 1N5376CTR | TRANS PNP HG -15V -2000MA TO-92 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TZA1048 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:4-channel BTL driver for CD/DVD drives |

| TZA1048TH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:4-channel BTL driver for CD/DVD drives |

| TZA10-5 | 制造商:RHOMBUS-IND 制造商全稱:Rhombus Industries Inc. 功能描述:TZA / TYA Series 5-Tap High Performance Passive Delay Modules |

| TZA10-7 | 制造商:RHOMBUS-IND 制造商全稱:Rhombus Industries Inc. 功能描述:TZA / TYA Series 5-Tap High Performance Passive Delay Modules |

| TZA1-10 | 制造商:RHOMBUS-IND 制造商全稱:Rhombus Industries Inc. 功能描述:TZA / TYA Series 5-Tap High Performance Passive Delay Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。