- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359310 > uPSD3412C-40U6T (意法半導(dǎo)體) 320 x 240 pixel format, CFL backlight available with power harness PDF資料下載

參數(shù)資料

| 型號: | uPSD3412C-40U6T |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 320 x 240 pixel format, CFL backlight available with power harness |

| 中文描述: | 閃存可編程系統(tǒng)設(shè)備與8032微控制器核心和16Kbit SRAM的 |

| 文件頁數(shù): | 93/152頁 |

| 文件大?。?/td> | 1558K |

| 代理商: | UPSD3412C-40U6T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當(dāng)前第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁

93/152

UPSD3212C, UPSD3212CV

SRAM

The SRAM is enabled when SRAM Select (RS0)

from the DPLD is High. SRAM Select (RS0) can

contain up to two product terms, allowing flexible

memory mapping.

The SRAM can be backed up using an external

battery. The external battery should be connected

to Voltage Standby (V

STBY

, PC2). If you have an

external battery connected to the uPSD3200, the

contents of the SRAM are retained in the event of

a power loss. The contents of the SRAM are re-

tained so long as the battery voltage remains at 2V

or greater. If the supply voltage falls below the bat-

tery voltage, an internal power switchover to the

battery occurs.

PC4 can be configured as an output that indicates

when power is being drawn from the external bat-

tery. Battery-on Indicator (V

BATON

, PC4) is High

with the supply voltage falls below the battery volt-

age and the battery on Voltage Standby (V

STBY

,

PC2) is supplying power to the internal SRAM.

SRAM Select (RS0), Voltage Standby (V

STBY

,

PC2) and Battery-on Indicator (V

BATON

, PC4) are

all configured using PSDsoft Express Configura-

tion.

Sector Select and SRAM Select

Sector Select (FS0-FS3, CSBOOT0-CSBOOT1)

and SRAM Select (RS0) are all outputs of the

DPLD. They are setup by writing equations for

them in PSDsoft Express. The following rules ap-

ply to the equations for these signals:

1. Primary Flash memory and secondary Flash

memory Sector Select signals must not

be larg-

er than the physical sector size.

2. Any primary Flash memory sector must not

be

mapped in the same memory space as another

Flash memory sector.

3. A secondary Flash memory sector must not

be

mapped in the same memory space as another

secondary Flash memory sector.

4. SRAM, I/O, and Peripheral I/O spaces must not

overlap.

5. A secondary Flash memory sector may

overlap

a primary Flash memory sector. In case of over-

lap, priority is given to the secondary Flash

memory sector.

6. SRAM, I/O, and Peripheral I/O spaces may

overlap any other memory sector. Priority is giv-

en to the SRAM, I/O, or Peripheral I/O.

Example.

FS0 is valid when the address is in the

range of 8000h to BFFFh, CSBOOT0 is valid from

8000h to 9FFFh, and RS0 is valid from 8000h to

87FFh. Any address in the range of RS0 always

accesses the SRAM. Any address in the range of

CSBOOT0 greater than 87FFh (and less than

9FFFh) automatically addresses secondary Flash

memory segment 0. Any address greater than

9FFFh accesses the primary Flash memory seg-

ment 0. You can see that half of the primary Flash

memory segment 0 and one-fourth of secondary

Flash memory segment 0 cannot be accessed in

this example.

Note:

An equation that defined FS1 to anywhere

in the range of 8000h to BFFFh would not

be valid.

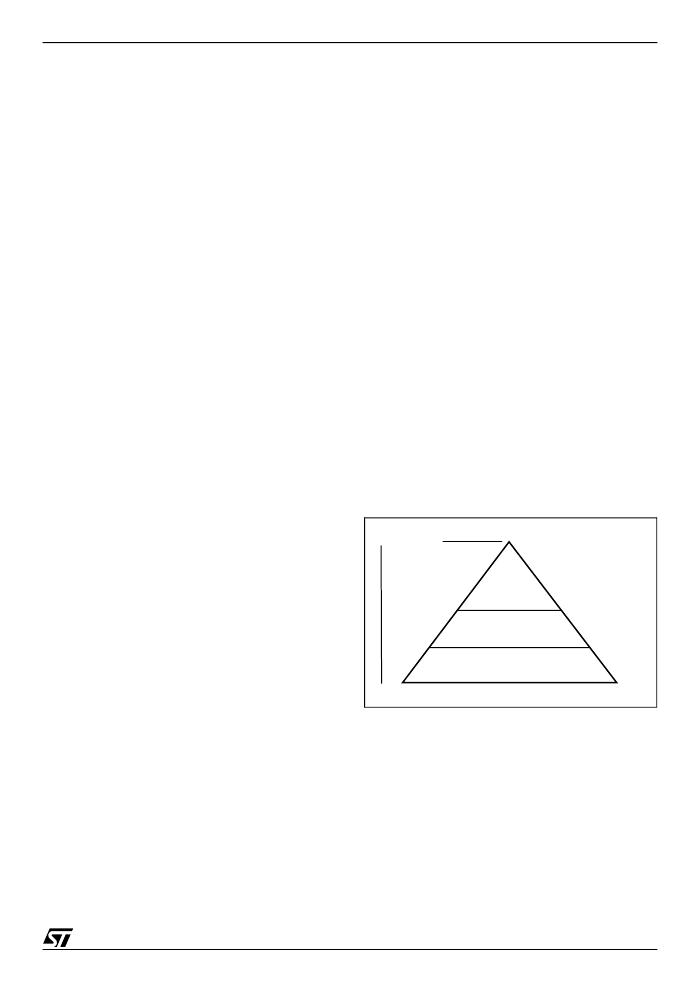

Figure 44 shows the priority levels for all memory

components. Any component on a higher level can

overlap and has priority over any component on a

lower level. Components on the same level must

not

overlap. Level one has the highest priority and

level 3 has the lowest.

Figure 44. Priority Level of Memory and I/O

Components in the PSD MODULE

Level 1

SRAM, I/O, or

Peripheral I/O

Level 2

Secondary

Non-Volatile Memory

Highest Priority

Lowest Priority

Level 3

Primary Flash Memory

AI02867D

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPSD3433EV-40U6 | Turbo Plus Series Fast Turbo 8032 MCU with USB and Programmable Logic |

| UR132-26-AE3-5-R | 200mA LOW DROPOUT LINEAR VOLTAGE REGULATOR |

| URS1A101MRD | ALUMINUM ELECTROLYTIC CAPACITORS |

| URU1V470MRD | ALUMINUM ELECTROLYTIC CAPACITORS |

| URZ1A101MPD | ALUMINUM ELECTROLYTIC CAPACITORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPSD3422E-40T6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422E-40U6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EB40T6 | 功能描述:8位微控制器 -MCU Turbo 8032 MCU w/USB & Programmable Logic RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EB40U6 | 功能描述:8位微控制器 -MCU uPSD34x Turbo Plus Fast Turbo 8032 MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| UPSD3422EV-40T6 | 功能描述:8位微控制器 -MCU 8 BITS MICROCONTR RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。