- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68459 > W6692ACF (WINBOND ELECTRONICS CORP) DATACOM, ISDN CONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | W6692ACF |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | DATACOM, ISDN CONTROLLER, PQFP100 |

| 封裝: | QFP-100 |

| 文件頁數(shù): | 71/98頁 |

| 文件大小: | 584K |

| 代理商: | W6692ACF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁當前第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

Data Sheet

W6692A PCI ISDN S/T-Controller

Publication Release Date:

Mar,2000

Revision 1.0

-73 -

0: Transparent mode. In receive direction, address comparison is performed on each frame. The frames with matched

address are stored in B1_RFIFO. Flag deletion, CRC check and zero bit deletion are performed. In transmit direction, the data is

transmitted with flag insertion, zero bit insertion and CRC generation.

1: Extended transparent mode. In receive direction, all data are received and stored in the B1_RFIFO. In transmit

direction, all data in the B1_XFIFO are transmitted without alteration.

ITF

Inter-frame Time Fill

Defines the inter-frame time fill pattern in transparent mode.

0 : Mark. The binary value "1" is transmitted.

1 : Flag. This is a sequence of

"01111110".

EPCM

Enable PCM Transmit/Receive

0 : Disable data transmit/ receive to/from PCM port. The frame synchronization clock PFCK1 is held LOW.

1 : Enable data transmit/ receive to/from PCM port. The frame synchronization clock PFCK1 is active.

B1_SW1-0

B Channel Switching Select

These two bits, along with PXC bit in PCTL register, determine the connection in B1 channel. See section 7.4 for details.

Note: The connection with micro-controller is through HDLC controller. When HDLC connects with layer 1, either transparent

or extended transparent mode can be used. When HDLC connects with PCM port/GCI bus, only extended transparent mode can

be used and the EPCM bit must be set to enable PCM function.

SW56

Switch 56 Traffic

0: The data rate in B1 channel is 64 kbps.

1: The data rate in B1 channel is 56 kbps. The most significant bit in each octet is fixed at

"1".

Note: In 56 kbps mode, only transparent mode can be used.

FTS1-0

FIFO Threshold Select

These two bits determine the B1 channel receive and transmit FIFO's threshold setting. An interrupt is generated when the

number of received data or the number of vacancies in XFIFO reaches the threshold value.

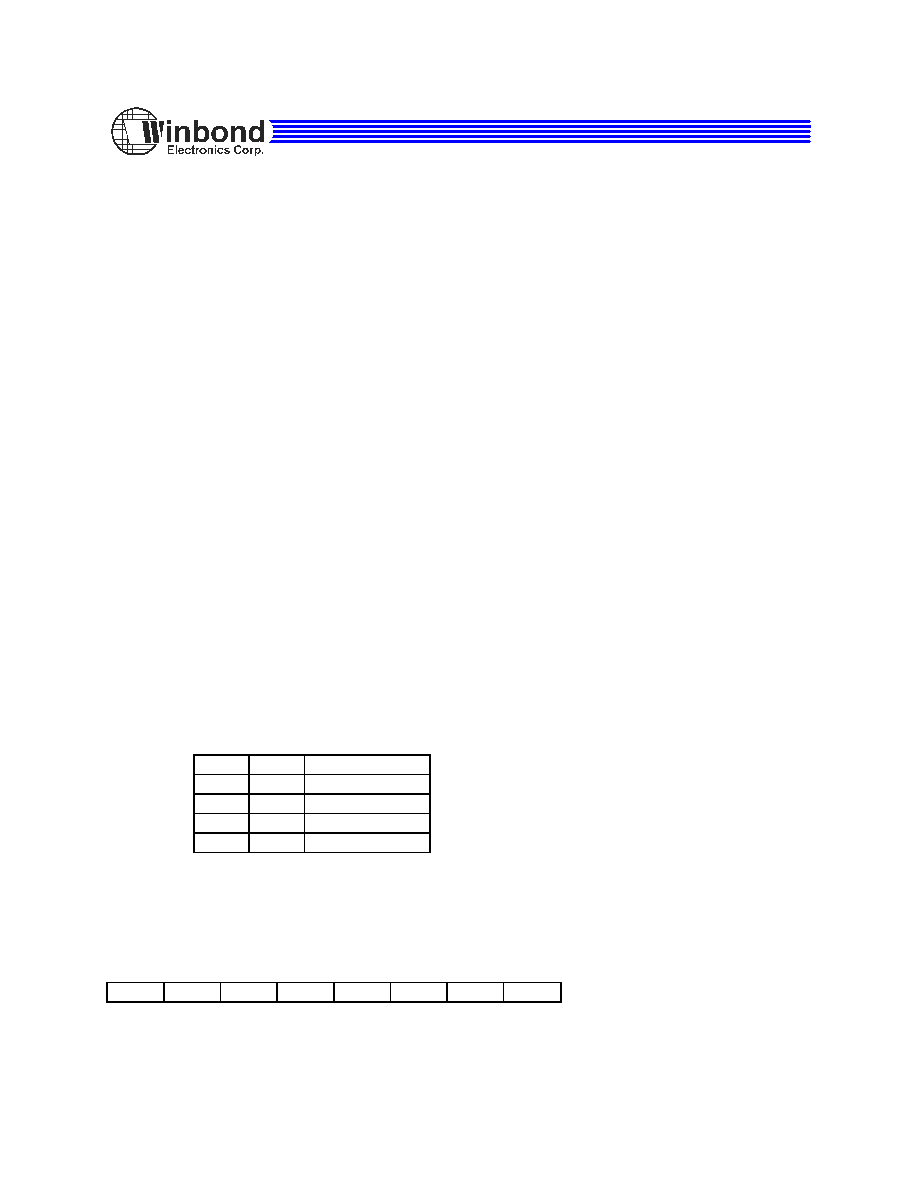

FTS1

FTS0

Threshold (byte)

0

64

0

1

Reserved

1

0

96

1

Not allowed

8.2.5 B1_ch Extended Interrupt Register B1_EXIR

Read_clear

Address 90H/24H

Value after reset: 00H

7

6

5

4

3

2

1

0

RMR

RME

RDOV

XFR

XDUN

相關PDF資料 |

PDF描述 |

|---|---|

| W6694ACD | DATACOM, ISDN CONTROLLER, PQFP48 |

| W671320P | TELECOM-SLIC, PQCC28 |

| W671361P | TELECOM-SLIC, PQCC28 |

| W671361Y | TELECOM-SLIC, QCC32 |

| W671310P | TELECOM-SLIC, PQCC28 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| W6694 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:USB Bus ISDN S/T-Controller |

| W6694A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TE Mode S/T Controller with USB 1.1 Interface |

| W6694CD | 制造商:WINBOND 制造商全稱:Winbond 功能描述:USB Bus ISDN S/T-Controller |

| W66ARX-18 | 制造商:Magnecraft 功能描述: |

| W66MAF185X | 制造商:Panasonic Industrial Company 功能描述:CRT |

發(fā)布緊急采購,3分鐘左右您將得到回復。