- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361790 > W6694CD (WINBOND ELECTRONICS CORP) USB Bus ISDN S/T-Controller PDF資料下載

參數(shù)資料

| 型號(hào): | W6694CD |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | USB Bus ISDN S/T-Controller |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP48 |

| 封裝: | 7 X 7 MM, 1.40 MM, PLASTIC, LQFP-48 |

| 文件頁(yè)數(shù): | 13/42頁(yè) |

| 文件大小: | 567K |

| 代理商: | W6694CD |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

Preliminary Data Sheet

W6694A USB-ISDN S/T-Controller

-13-

Publication Release Date: May, 2001

Revision 1.03

7. FUNCTIONAL DESCRIPTIONS

7.1 Microcontroller

The embedded 8 bit microcontroller core is a standard 80C51 MCU, operate at 24 MHz clock frequency. Its main function is

to transparently transfer data between USB, and ISDN/GCI/PCM interface. Data in D/B1/B2 channel is transferred as it is,

without further HDLC framing processing. All interface accept D/B1/B2 channel data, except for PCM interface, which

accept only B channel data. The data from each interface is first stored at individual register in the SFR (Special Function

Register) of microcontroller. Then the firmware, which resides in internal Mask ROM, is executed to constantly move data

between registers for different interface. The B channel receiving registers can be programmed by way of USB interface to

dynamically assign the data path between interfaces.

7.1.1 Special function register (SFR)

The SFRs, as in standard 80C51 architecture, reside in the upper 128 bytes of internal RAM, from address 80H to FFH.

W6694A specifically assign registers among SFRs exclusively for use of internal data transfer between interfaces. SFRs are

accessed by internal firmware only, and cannot be directly accessed by Bulk-OUT commands of USB interface. However,

some of the Bulk-OUT commands are used by host software to control FIFOs, such as CMDR1 and CMDR2.

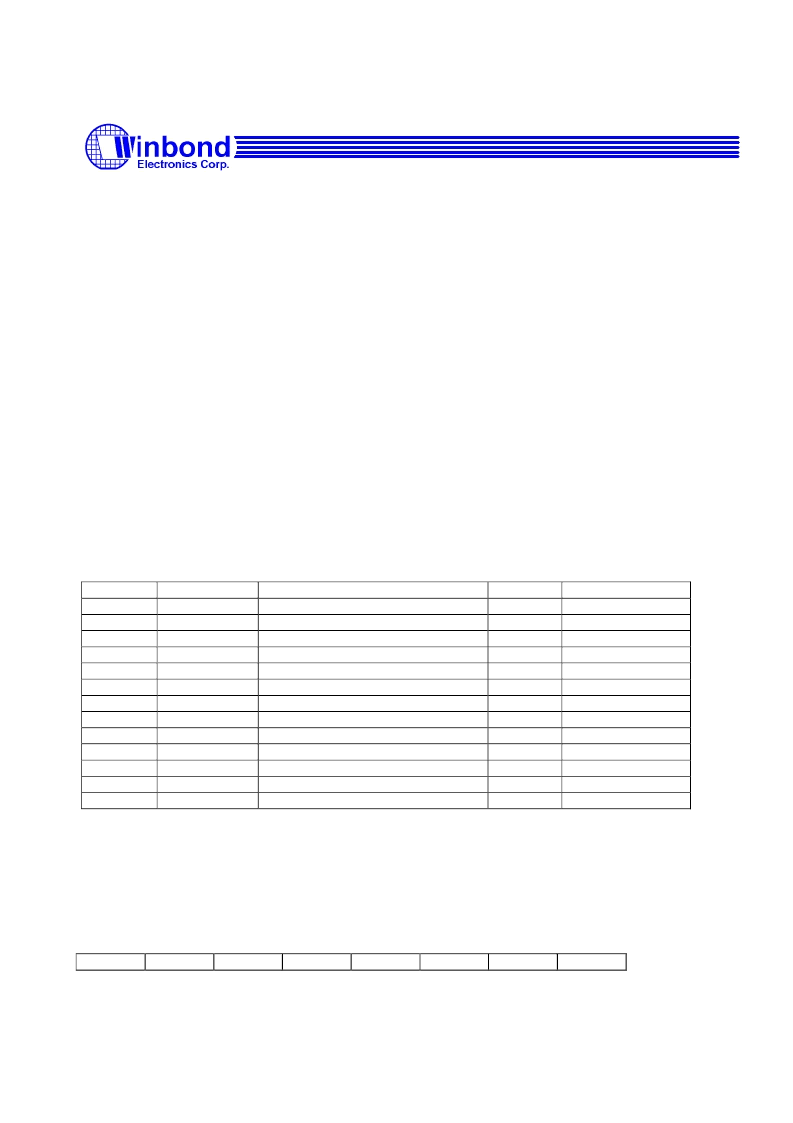

TAble 7.1 W6694A specified SFR

SFR Addr.

C0

C1

C2

C3

C4

C5

C6

C9

CA

CB

CC

CD

CE

The reset values of above registers are all 0.

Symbol

INTFS

L1DDR

L1DDW

CB1DR

CB1DW

CB2DR

CB2DW

USBDDR

USBDDW

USBB1DR

USBB1DW

USBB2DR

USBB2DW

Meaning

Interface Status

Layer 1 D Channel Data Read

Layer 1 D Channel Data Write

Common B 1 Channel Data Read

Common B 1 Channel Data Write

Common B 2 Channel Data Read

Common B 2 Channel Data Write

USB D Channel Data Read

USB D Channel Data Write

USB B 1 Channel Data Read

USB B 1 Channel Data Write

USB B 2 Channel Data Read

USB B 2 Channel Data Write

Access

R

R

W

R

W

R

W

R

W

R

W

R

W

Bit Addressable

Yes

No

No

No

No

No

No

No

No

No

No

No

No

7.1.1.1 Interface Status Register

Values after reset: 00h

7

6

L1DRR

L1DWR

INTFS

Read_clear

Address C0h

5

4

3

2

1

0

CB1RR

CB1WR

CB2RR

CB2WR

UDRR

UDWR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W7020 | Telecommunication IC |

| W722 | Controller Miscellaneous - Datasheet Reference |

| W72963APOLLOELITE | BEWEGUNGSMELDER IR REICHW 12M |

| W72M64V-XBX | Flash MCP |

| W72M64VK120BM | 2Mx64 3.3V Simultaneous Operation Flash Multi-Chip Package |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W66ARX-18 | 制造商:Magnecraft 功能描述: |

| W66MAF185X | 制造商:Panasonic Industrial Company 功能描述:CRT |

| W66R_1G WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| W66TX-25 | 制造商:Magnecraft 功能描述: |

| W66TX-29 | 制造商:Magnecraft 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。