- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361790 > W6694CD (WINBOND ELECTRONICS CORP) USB Bus ISDN S/T-Controller PDF資料下載

參數(shù)資料

| 型號: | W6694CD |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | USB Bus ISDN S/T-Controller |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP48 |

| 封裝: | 7 X 7 MM, 1.40 MM, PLASTIC, LQFP-48 |

| 文件頁數(shù): | 27/42頁 |

| 文件大小: | 567K |

| 代理商: | W6694CD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Preliminary Data Sheet

W6694A USB-ISDN S/T-Controller

-27-

Publication Release Date: May, 2001

Revision 1.03

Setting this bit activates the remote loop back function. The received 2B channels from the S/T interface are looped

to the transmitted 2B channels of S/T interface. The D channel is not looped in this loop back function.

This bit remains set, until cleared by software reset (SRST).

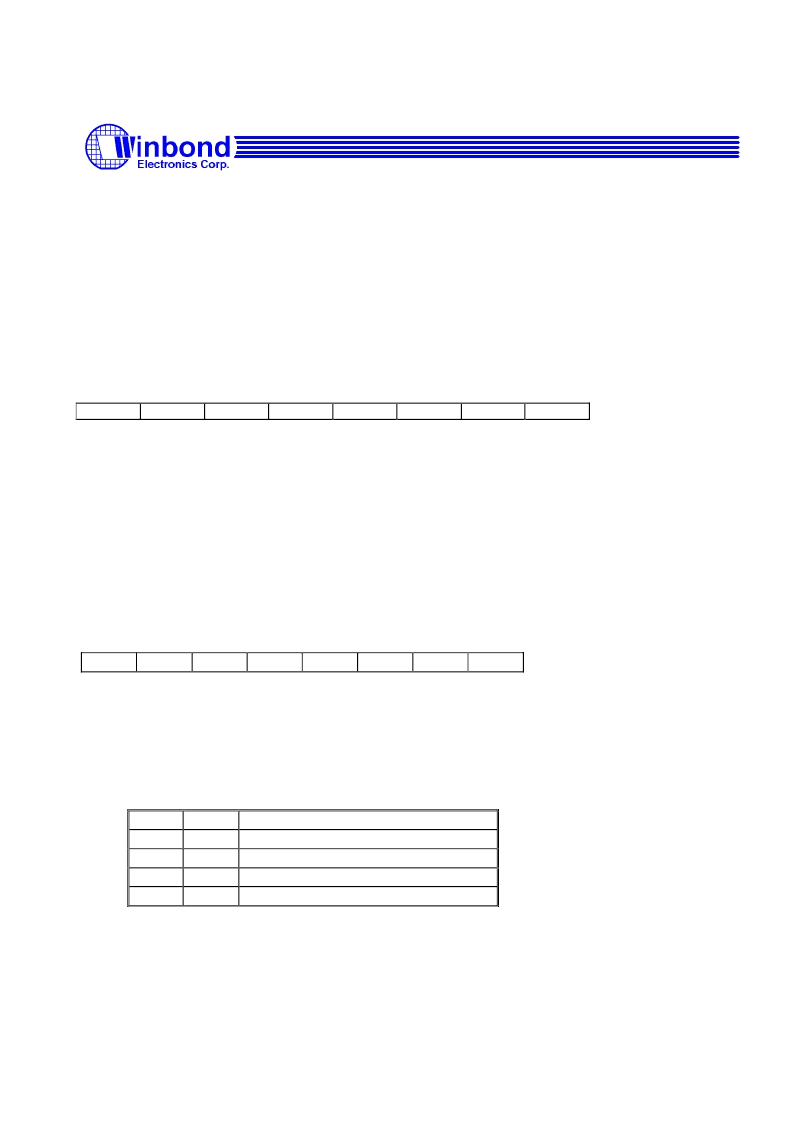

8.2.3 Command Register 2

Value after reset: 00h

Bits in this register act similar to that of CMDR1 register, except that the effect is on B1 or B2 channel XFIFO/RFIFO,

instead of on D channel XFIFO/RFIFO.

7

6

5

4

3

B1XRST

B1RRST

B1XEN

B1REN

B2XRST

B1XRST

B1 Channel Transmitter Reset

B1RRST

B1 Channel Receiver Reset

B1XEN

B1 Channel Transmit FIFO Enable

B1REN

B1 Channel Receive FIFO Enable

B2XRST

B2 Channel Transmitter Reset

B2RRST

B2 Channel Receiver Reset

B2XEN

B2 Channel Transmit FIFO Enable

B2REN

B2 Channel Receive FIFO Enable

CMDR2

Write

Address 02h

2

1

0

B2RRST

B2XEN

B2REN

8.2.4 Control Register

Value after reset : 00H

7

BAM

BAM

B Channel Auto Mode

This mode let hardware automatically enable B1 or B2 channel transmit FIFO (XFIFO), whenever there is any error

occurred for B channel XFIFO. No B channel XFIFO error status is reported to USB host. Writing 0 to this bit

disable auto mode.

OPS1-0 Output Phase Delay Compensation Select1-0

These two bits select the output phase delay compensation.

OPS1

OPS0 Effect

0

0

No output phase delay compensation

0

1

Output phase delay compensation 260ns

1

0

Output phase delay compensation 520 ns

1

1

Output phase delay compensation 1040 ns

CTL

Read/Write Address 03h

6

0

5

0

4

0

3

0

2

0

1

0

OPS1

OPS0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W7020 | Telecommunication IC |

| W722 | Controller Miscellaneous - Datasheet Reference |

| W72963APOLLOELITE | BEWEGUNGSMELDER IR REICHW 12M |

| W72M64V-XBX | Flash MCP |

| W72M64VK120BM | 2Mx64 3.3V Simultaneous Operation Flash Multi-Chip Package |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W66ARX-18 | 制造商:Magnecraft 功能描述: |

| W66MAF185X | 制造商:Panasonic Industrial Company 功能描述:CRT |

| W66R_1G WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| W66TX-25 | 制造商:Magnecraft 功能描述: |

| W66TX-29 | 制造商:Magnecraft 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。