- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202121 > WV3EG128M72EFSR262D3MG (WHITE ELECTRONIC DESIGNS CORP) 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 PDF資料下載

參數(shù)資料

| 型號: | WV3EG128M72EFSR262D3MG |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | DRAM |

| 英文描述: | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| 封裝: | ROHS COMPLIANT, DIMM-184 |

| 文件頁數(shù): | 12/13頁 |

| 文件大小: | 382K |

| 代理商: | WV3EG128M72EFSR262D3MG |

8

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

March 2005

Rev. 0

ADVANCED

WV3EG128M72EFSR-D3

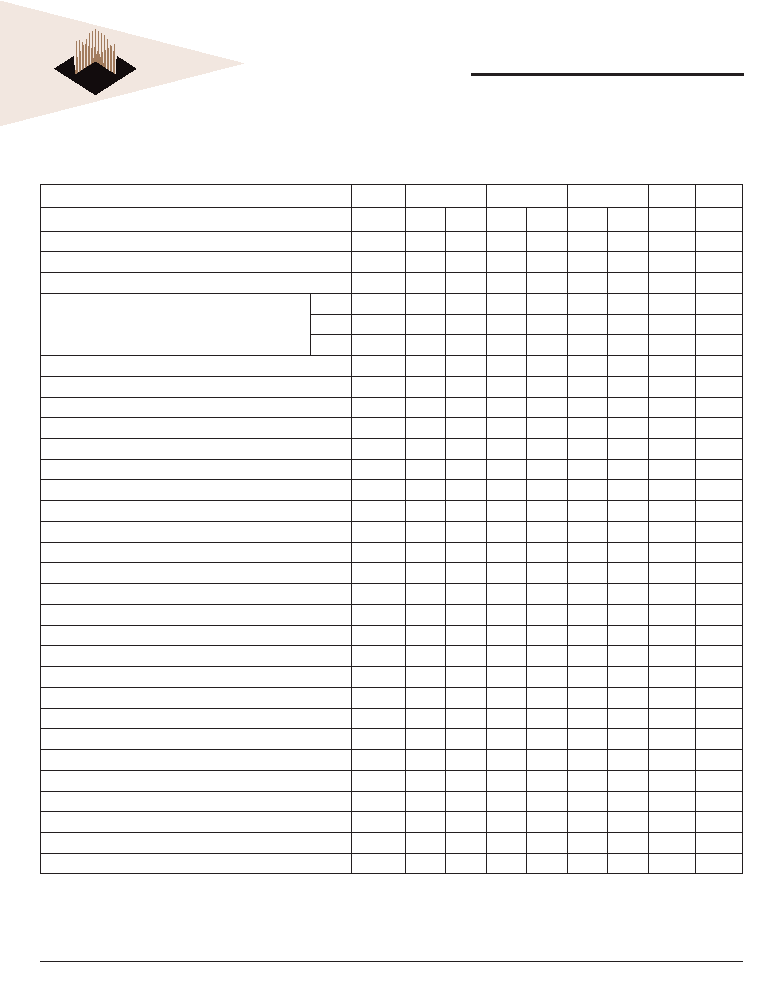

DDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS AND

RECOMMENDED AC OPERATING CONDITIONS

0°C ≤ TA ≤ +70°C; VCC = +2.5V ±0.2V, VCCQ = +2.5V ±0.2V

AC Characteristics

335

262

265

Parameter

Symbol

Min

Max

Min

Max

Min

Max

Units

Notes

Access window of DQs from CK, CK#

tAC

-0.7

+0.7

-0.75

+0.75

-0.75

+0.75

ns

CK high-level width

tCH

0.45

0.55

0.45

0.55

0.45

0.55

tCK

16

CK low-level width

tCL

0.45

0.55

0.45

0.55

0.45

0.55

tCK

16

Clock cycle time

CL=3

tCK (3)

6

13

7.5

13

7.5

13

ns

22

CL=2.5 tCK (2.5)

6

12

7.5

12

7.5

12

ns

22

CL=2

tCK (2)

7.5

12

7.5

12

10

12

ns

22

DQ and DM input hold time relative to DQS

tDH

0.45

0.5

ns

14,17

DQ and DM input setup time relative to DQS

tDS

0.45

0.5

ns

14,17

DQ and DM input pulse width (for each input)

tDIPW

1.75

ns

17

Access window of DQS from CK, CK#

tDQSCK

-0.6

+0.6

-0.75

+0.75

-0.75

+0.75

ns

DQS input high pulse width

tDQSH

0.35

tCK

DQS input low pulse width

tDQSL

0.35

tCK

DQS-DQ skew, DQS to last DQ valid, per group, per access

tDQSQ

0.4

0.5

ns

13,14

Write command to rst DQS latching transition

tDQSS

0.75

1.25

0.75

1.25

0.75

1.25

tCK

DQS falling edge to CK rising - setup time

tDSS

0.2

tCK

DQS falling edge from CK rising - hold time

tDSH

0.2

tCK

Half clock period

tHP

tCH, tCL

ns

18

Data-out high-impedance window from CK, CK#

tHZ

+0.7

+0.75

ns

8,19

Data-out low-impedance window from CK, CK#

tLZ

-0.7

-0.75

ns

8,20

Address and control input hold time (fast slew rate)

tIHf

0.75

0.90

ns

6

Address and control input set-up time (fast slew rate)

tISf

0.75

0.90

ns

6

Address and control input hold time (slow slew rate)

tIHs

0.8

1

ns

6

Address and control input setup time (slow slew rate)

tISs

0.8

1

ns

6

Address and control input pulse width (for each input)

tIPW

2.2

ns

LOAD MODE REGISTER command cycle time

tMRD

12

15

ns

DQ-DQS hold, DQS to rst DQ to go non-valid, per access

tQH

tHP-tQHS

ns

13,14

Data hold skew factor

tQHS

0.55

0.75

ns

ACTIVE to PRECHARGE command

tRAS

42

70,000

45

120,000

45

120,000

ns

15

ACTIVE to READ with Auto precharge command

tRAP

18

15

20

ns

ACTIVE to ACTIVE/AUTO REFRESH command period

tRC

60

65

ns

AUTO REFRESH command period

tRFC

72

75

ns

21

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W7NCF08GH10CS4FM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10CSA5DM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10IS8BM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10ISA4HM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10ISA7AM1G | FLASH 3.3V PROM MODULE, XMA50 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| WV3EG128M72EFSR262D3SF | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

| WV3EG128M72EFSR262D3SG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

| WV3EG128M72EFSR265D3MF | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

| WV3EG128M72EFSR265D3MG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

| WV3EG128M72EFSR265D3SF | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。