- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202121 > WV3EG128M72EFSR262D3MG (WHITE ELECTRONIC DESIGNS CORP) 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 PDF資料下載

參數(shù)資料

| 型號: | WV3EG128M72EFSR262D3MG |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | DRAM |

| 英文描述: | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| 封裝: | ROHS COMPLIANT, DIMM-184 |

| 文件頁數(shù): | 8/13頁 |

| 文件大?。?/td> | 382K |

| 代理商: | WV3EG128M72EFSR262D3MG |

4

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

March 2005

Rev. 0

ADVANCED

WV3EG128M72EFSR-D3

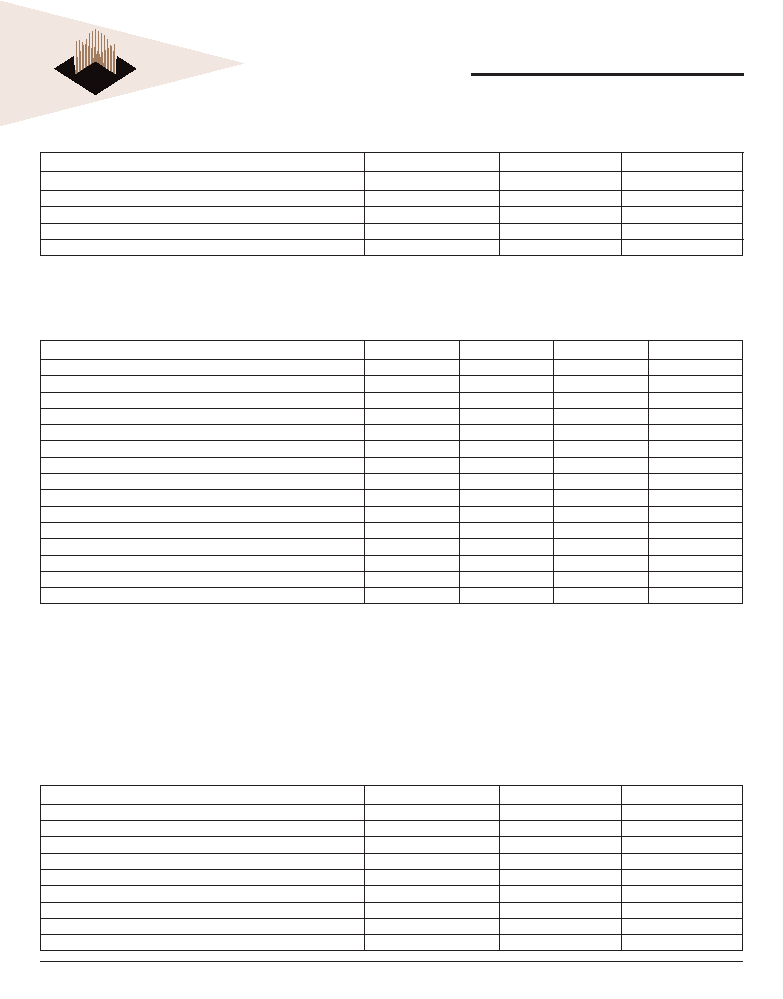

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Value

Units

Voltage on any pin relative to VSS

VIN, VOUT

-0.5 to 3.6

V

Voltage on VCC supply relative to VSS

VCC, VCCQ

-1.0 to 3.6

V

Storage Temperature

TSTG

-55 to +150

°C

Power Dissipation

PD

18

W

Short Circuit Current

IOS

50

mA

Note:

Permanent device damage may occur if ‘ABSOLUTE MAXIMUM RATINGS’ are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability

DC CHARACTERISTICS

0°C TA 70°C, VCC = 2.5V ± 0.2V

Parameter

Symbol

Min

Max

Unit

Supply Voltage (for device with nominal VCC of 2.5V)

VCC

2.3

V

I/O Supply Voltage

VCCQ

2.3

V

I/O Reference Voltage

VREF

VCCQ/2-50mV

VCCQ/2+50mV

V

I/O Termination Voltage (systems)

VTT

VREF -0.04

VREF +0.04

V

Input Logic High Voltage

VIH(DC)

VREF +0.15

VCCQ +0.3

V

Input Logic Low Voltage

VIL(DC)

-0.3

VREF -0.15

V

Input Voltage Level, CK and CK# inputs

VIN(DC)

-0.3

VCCQ +0.3

V

Input Differential Voltage, CK and CK# inputs

VID(DC)

0.3

VCCQ +0.6

V

Input Crossing Point Voltage, CK and CK# inputs

VIX(DC)

1.15

1.35

V

Input Leakage Current

IL

-2

2

uA

Output Leakage Current

IOZ

-5

5

uA

Output High Current (Normal strength driver); VOUT = VTT + 0.84V

IOH

-16.8

mA

Output High Current (Normal strength driver); VOUT = VTT - 0.84V

IOL

16.8

mA

Output High Current (Half strength driver); VOUT = VTT + 0.45V

IOH

-9

mA

Output High Current (Half strength driver); VOUT = VTT - 0.45V

IOL

9mA

CAPACITANCE

TA = 25°C. f = 1MHz, VCC = 2.5V

Parameter

Symbol

Max

Unit

Input Capacitance (A0-A12)

CIN1

11

pF

Input Capacitance (RAS#, CAS#, WE#)

CIN2

11

pF

Input Capacitance (CKE0, CKE1)

CIN3

11

pF

Input Capacitance (CK0#, CK0)

CIN4

12

pF

Input Capacitance (CS0#, CS1#)

CIN5

11

pF

Input Capacitance (DQM0-DQM8)

CIN6

15

pF

Input Capacitance (BA0-BA1)

CIN7

11

pF

Data input/output capacitance (DQ0-DQ63)(DQS)

COUT

15

pF

Data input/output capacitance (CB0-CB7)

COUT

15

pF

Notes:

1.

Includes ± 25mV margin for DC offset on VREF, and a combined total of ± 50mV

margin for all AC noise and DC offset on VREF, bandwidth limited to 20MHz. The

DRAM must accommodate DRAM current spikes on VREF and internal DRAM

noise coupled TO VREF, both of which may result in VREF noise. VREF should be

de-coupled with an inductance of ≤ 3nH.

2.

VTT is not applied directly to the device. VTT is a system supply for signal

termination resistors, is expected to be set equal to VREF, and must track variations

in the DC level of VREF

3.

VID is the magnitude of the difference between the input level on CK and the input

level on CK#.

4.

These parameters should be tested at the pin on actual components and may

be checked at either the pin or the pad in simulation. The AC and DC input

specications are relative to a VREF envelop that has been bandwidth limited to

200MHZ.

5.

The value of VIX is expected to equal 0.5*VCCQ of the transmitting device and must

track variations in the dc level of the same.

6.

These charactericteristics obey the SSTL-2 class II standards.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W7NCF08GH10CS4FM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10CSA5DM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10IS8BM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10ISA4HM1G | FLASH 3.3V PROM MODULE, XMA50 |

| W7NCF08GH10ISA7AM1G | FLASH 3.3V PROM MODULE, XMA50 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| WV3EG128M72EFSR262D3SF | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

| WV3EG128M72EFSR262D3SG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

| WV3EG128M72EFSR265D3MF | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

| WV3EG128M72EFSR265D3MG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

| WV3EG128M72EFSR265D3SF | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:1GB - 128Mx72 DDR SDRAM REGISTERED w/PLL, FBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。