- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371258 > X4283 (Intersil Corporation) CPU Supervisor with 128K EEPROM PDF資料下載

參數(shù)資料

| 型號: | X4283 |

| 廠商: | Intersil Corporation |

| 元件分類: | DRAM |

| 英文描述: | CPU Supervisor with 128K EEPROM |

| 中文描述: | CPU監(jiān)控與128K的EEPROM的 |

| 文件頁數(shù): | 12/22頁 |

| 文件大?。?/td> | 412K |

| 代理商: | X4283 |

X4283/85 – Preliminary Information

Characteristics subject to change without notice.

12 of 22

REV 1.17 11/27/00

www.xicor.com

There is a similar operation, called “Set Current

Address” where the device does no operation, but

enters a new address into the address counter if a stop

is issued instead of the second start shown in Figure

13. The device goes into standby mode after the stop

and all bus activity will be ignored until a start is

detected. The next Current Address Read operation

reads from the newly loaded address. This operation

could be useful if the master knows the next address it

needs to read, but is not ready for the data.

Sequential Read

Sequential reads can be initiated as either a current

address read or random address read. The first Data

Byte is transmitted as with the other modes; however,

the master now responds with an acknowledge,

indicating it requires additional data. The device contin-

ues to output data for each acknowledge received. The

master terminates the read operation by not responding

with an acknowledge and then issuing a stop condition.

The data output is sequential, with the data from

address n followed by the data from address n + 1. The

address counter for read operations increments

through all page and column addresses, allowing the

entire memory contents to be serially read during one

operation. At the end of the address space the counter

“rolls over” to address 0000

H

and the device continues

to output data for each acknowledge received. Refer to

Figure 14 for the acknowledge and data transfer

sequence.

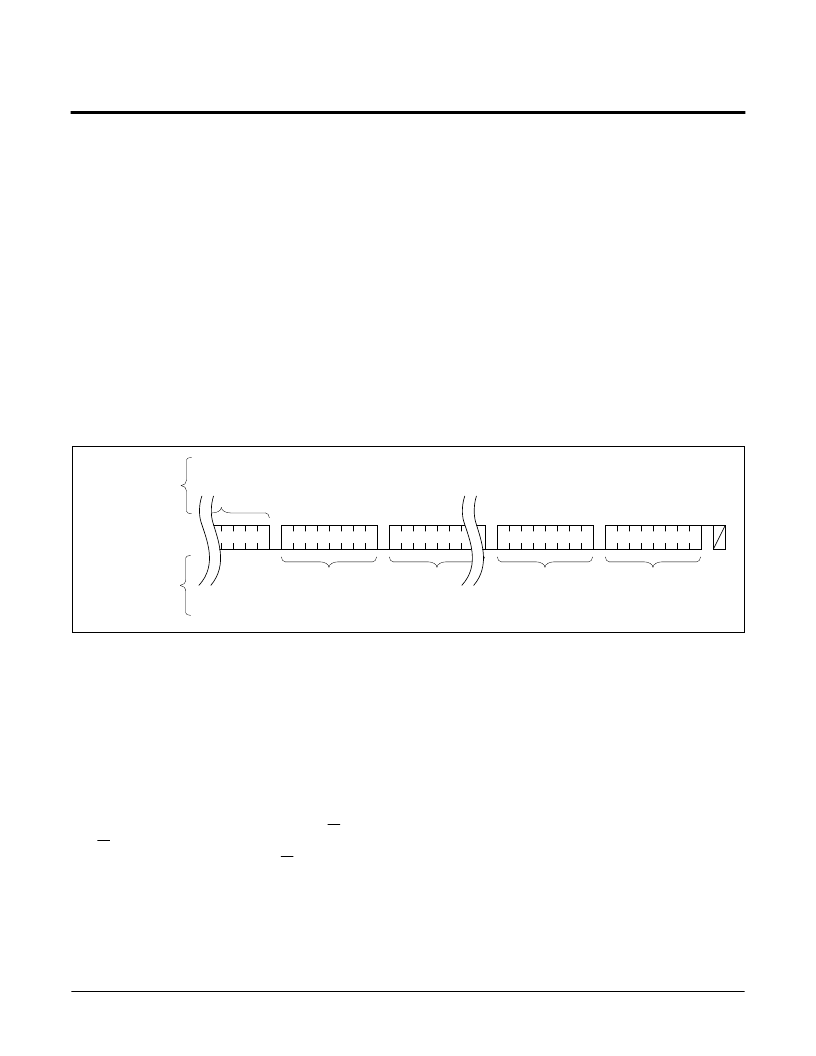

Figure 14. Sequential Read Sequence

Data

(2)

S

t

o

p

Slave

Address

Data

(n)

A

C

K

A

C

K

SDA Bus

Signals from

the Slave

Signals from

the Master

1

Data

(n-1)

A

C

K

A

C

K

(n is any integer greater than 1)

Data

(1)

X4283/85 Addressing

S

LAVE

A

DDRESS

B

YTE

Following a start condition, the master must output a

Slave Address Byte. This byte consists of several parts:

– a device type identifier that is ‘1010’ to access the array

– one bits of ‘0’.

– next two bits are the device address.

– one bit of the slave command byte is a R/W bit. The

R/W bit of the Slave Address Byte defines the opera-

tion to be performed. When the R/W bit is a one, then

a read operation is selected. A zero selects a write

operation. Refer to Figure 15.

– After loading the entire Slave Address Byte from the

SDA bus, the device compares the input slave byte

data to the proper slave byte. Upon a correct compare,

the device outputs an acknowledge on the SDA line.

Word Address

The word address is either supplied by the master or

obtained from an internal counter. The internal counter

is undefined on a power up condition.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X4283V8I-2.7A | CPU Supervisor with 128K EEPROM |

| X4285V8I-2.7A | CPU Supervisor with 128K EEPROM |

| X4285S8 | CPU Supervisor with 128K EEPROM |

| X4285V8 | CPU Supervisor with 128K EEPROM |

| X46402 | RTC Module With CPU Supervisor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X4283_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CPU Supervisor with 128K EEPROM |

| X4283AL | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:CPU Supervisor with 128K EEPROM |

| X4283AM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:CPU Supervisor with 128K EEPROM |

| X4283AN | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:CPU Supervisor with 128K EEPROM |

| X4283AP | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:CPU Supervisor with 128K EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。