- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371258 > X4283 (Intersil Corporation) CPU Supervisor with 128K EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | X4283 |

| 廠商: | Intersil Corporation |

| 元件分類(lèi): | DRAM |

| 英文描述: | CPU Supervisor with 128K EEPROM |

| 中文描述: | CPU監(jiān)控與128K的EEPROM的 |

| 文件頁(yè)數(shù): | 3/22頁(yè) |

| 文件大?。?/td> | 412K |

| 代理商: | X4283 |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

X4283/85 – Preliminary Information

Characteristics subject to change without notice.

3 of 22

REV 1.17 11/27/00

www.xicor.com

PRINCIPLES OF OPERATION

Power On Reset

Application of power to the X4283/85 activates a Power

On Reset Circuit that pulls the RESET/RESET pin

active. This signal provides several benefits.

– It prevents the system microprocessor from starting

to operate with insufficient voltage.

– It prevents the processor from operating prior to sta-

bilization of the oscillator.

– It allows time for an FPGA to download its configura-

tion prior to initialization of the circuit.

– It prevents communication to the EEPROM, greatly

reducing the likelihood of data corruption on power up.

When V

CC

exceeds the device V

for 200ms (nominal) the circuit releases RESET/

RESET allowing the system to begin operation.

TRIP

threshold value

LOW VOLTAGE MONITORING

During operation, the X4283/85 monitors the V

and asserts RESET/RESET if supply voltage falls

below a preset minimum V

signal prevents the microprocessor from operating in a

power fail or brownout condition. The RESET/RESET

signal remains active until the voltage drops below 1V.

It also remains active until V

V

TRIP

for 200ms.

CC

level

TRIP

. The RESET/RESET

CC

returns and exceeds

WATCHDOG TIMER

The Watchdog Timer circuit monitors the microproces-

sor activity by monitoring the SDA and SCL pins. The

microprocessor must toggle the SDA pin HIGH to LOW

periodically, while SCL is HIGH (this is a start bit) prior

to the expiration of the watchdog time out period to pre-

vent a RESET/RESET signal. The state of two nonvola-

tile control bits in the Status Register determine the

watchdog timer period. The microprocessor can change

these watchdog bits, or they may be “l(fā)ocked” by tying

the WP pin HIGH.

EEPROM INADVERTENT WRITE PROTECTION

When RESET/RESET goes active as a result of a low

voltage condition or Watchdog Timer Time-Out, any in-

progress communications are terminated. While

RESET/RESET is active, no new communications are

allowed and no nonvolatile write operation can start.

Non-volatile writes in-progress when RESET/RESET

goes active are allowed to finish.

Additional protection mechanisms are provided with

memory Block Lock and the Write Protect (WP) pin.

These are discussed elsewhere in this document.

V

CC

THRESHOLD RESET PROCEDURE

The X4283/85 is shipped with a standard V

old (V

TRIP

) voltage. This value will not change over nor-

mal operating and storage conditions. However, in

applications where the standard V

right, or if higher precision is needed in the V

value, the X4283/85 threshold may be adjusted. The

procedure is described below, and uses the application

of a nonvolatile control signal.

CC

thresh-

TRIP

is not exactly

TRIP

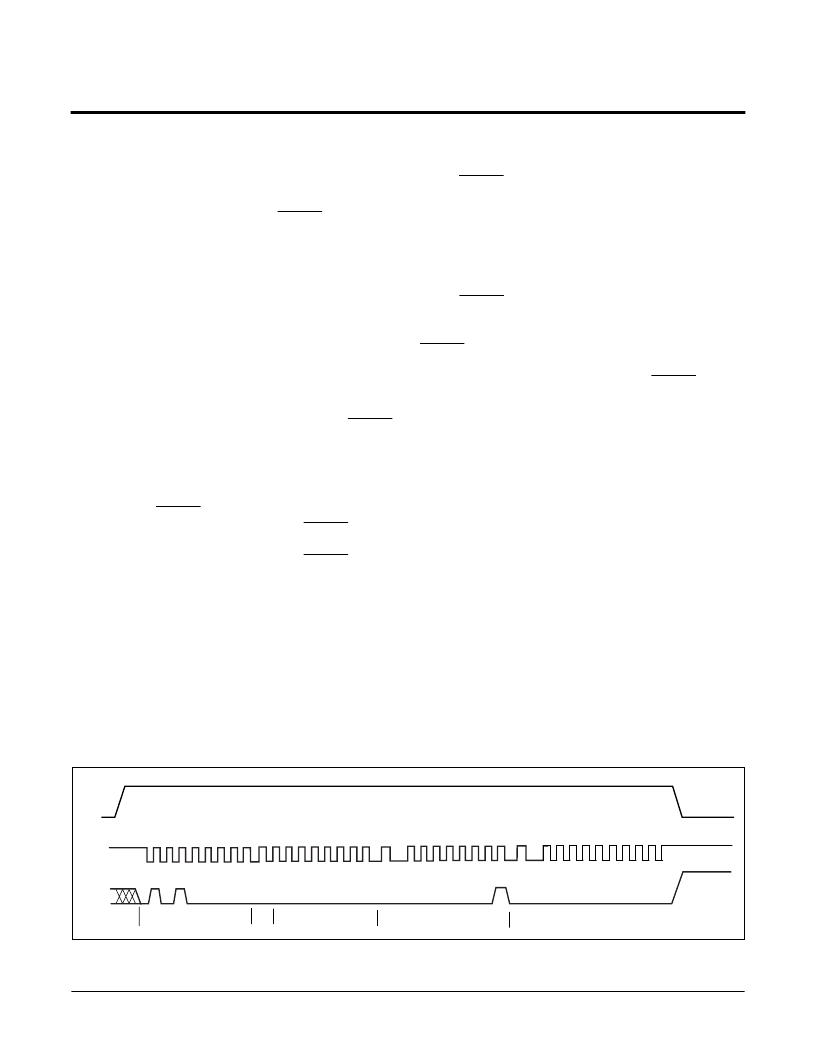

Figure 1. Set V

TRIP

Level Sequence (V

CC

= desired V

TRIP

values WEL bit set)

0 1 2 3 4 5 6 7

SCL

SDA

A0h

0 1 2 3 4 5 6 7

00h

WP

V

P

= 12-15V

0 1 2 3 4 5 6 7

01h

0 1 2 3 4 5 6 7

00h

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X4283V8I-2.7A | CPU Supervisor with 128K EEPROM |

| X4285V8I-2.7A | CPU Supervisor with 128K EEPROM |

| X4285S8 | CPU Supervisor with 128K EEPROM |

| X4285V8 | CPU Supervisor with 128K EEPROM |

| X46402 | RTC Module With CPU Supervisor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X4283_06 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:CPU Supervisor with 128K EEPROM |

| X4283AL | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:CPU Supervisor with 128K EEPROM |

| X4283AM | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:CPU Supervisor with 128K EEPROM |

| X4283AN | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:CPU Supervisor with 128K EEPROM |

| X4283AP | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:CPU Supervisor with 128K EEPROM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。